Dynamic Engineering News, Press Releases, Product Enhancements

Dynamic Engineering News

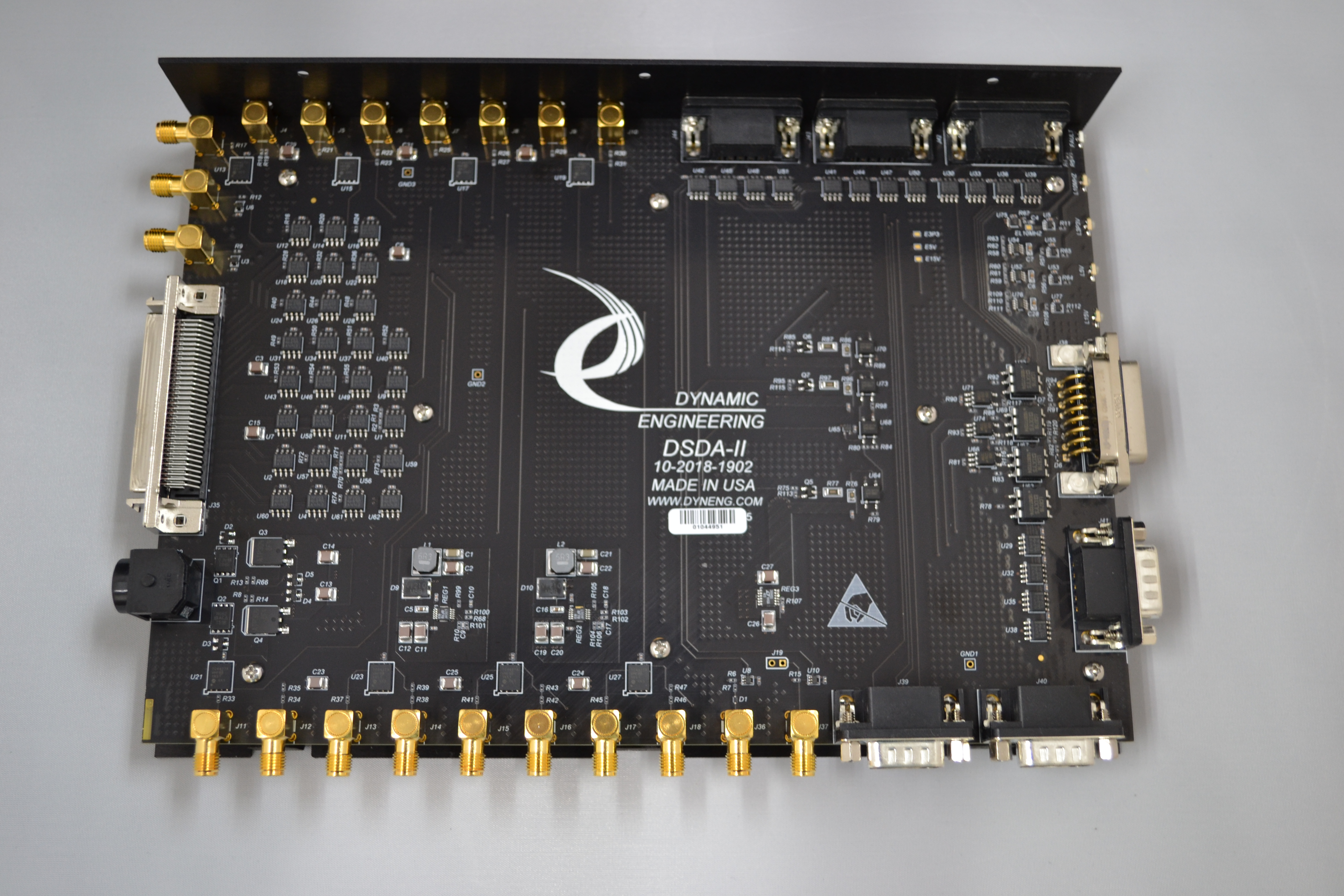

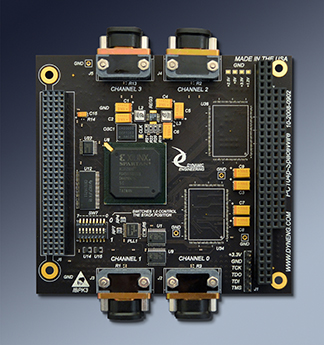

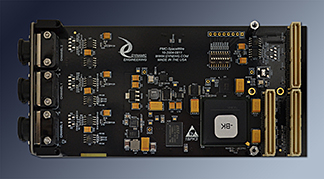

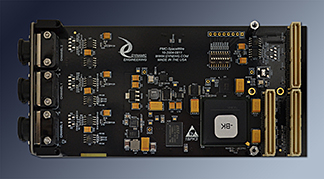

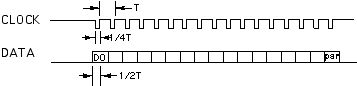

8 UART I/O ports each consisting of RS-485 transmit and receive data with RTS and CTS control. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock and up to 6 MBits with the PLL. Alternate reference frequencies are available. Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all ports. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. The -LM13 option selects an alternate FLASH installation with pinouts matching the Abaco / Radstone PMC-Q1F design. Options for Bezel and Rear IO.

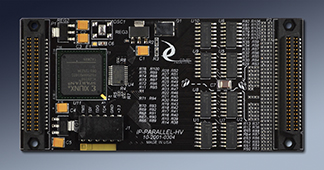

For ports selected to be in Parallel mode, each bit has separate control for direction, termination, Edge or Level, Interrupt enable, Rising Edge detection, Falling Edge detection, and polarity to allow flexible control over the interface. The driver supports all modes and the reference software demonstrates operation with COS interrupts etc.

Windows and Linux packages support all modes and come with reference SW. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab. Flash revision 3.1 or later is required for the parallel port option to be installed.

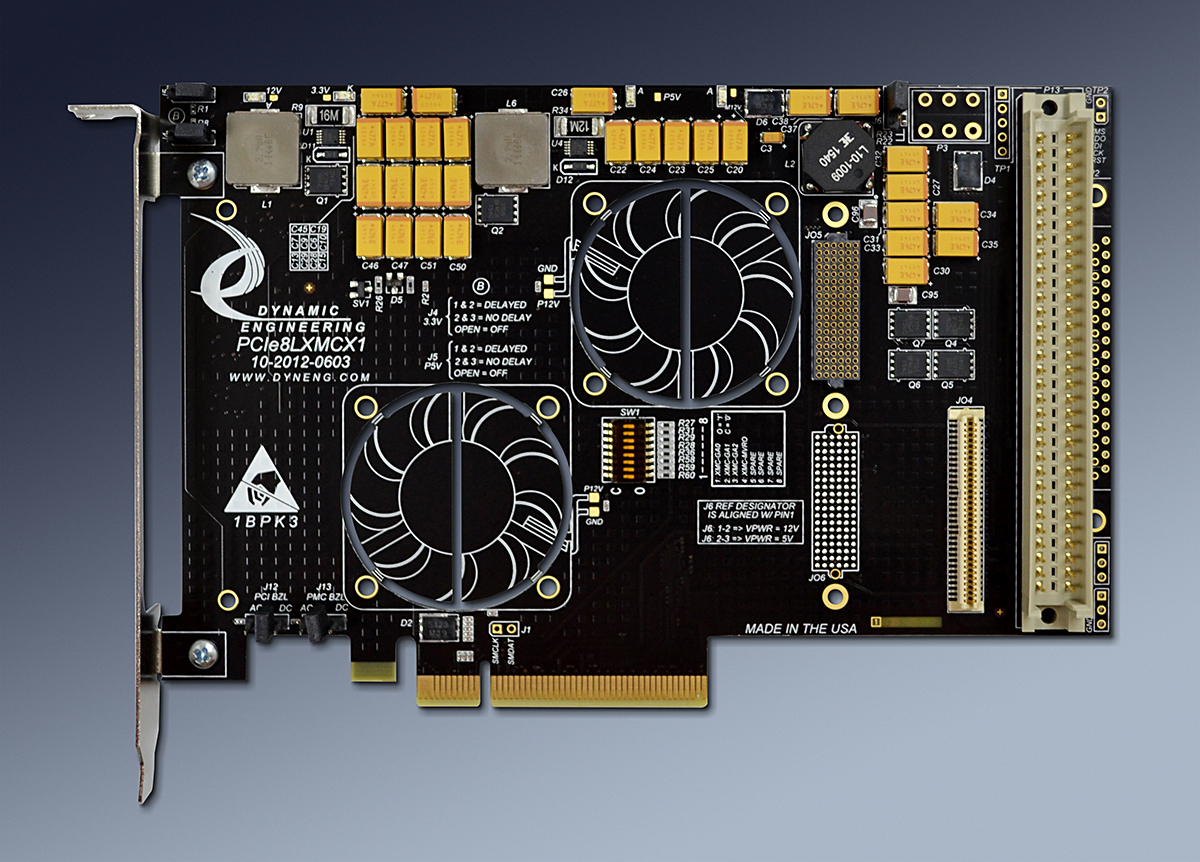

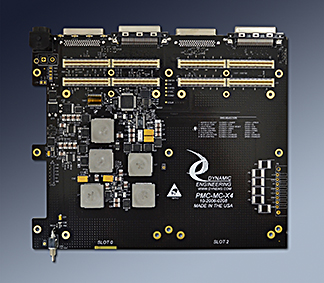

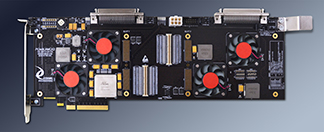

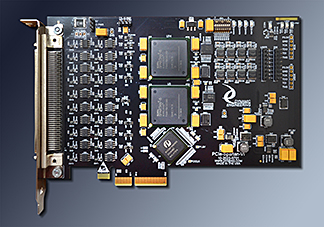

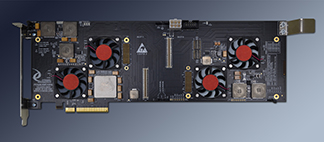

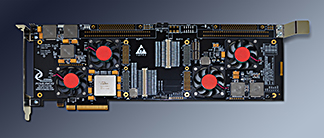

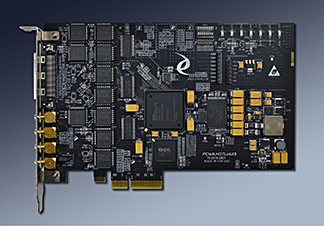

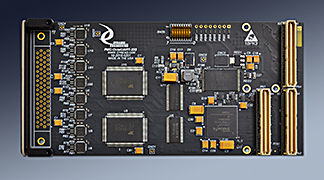

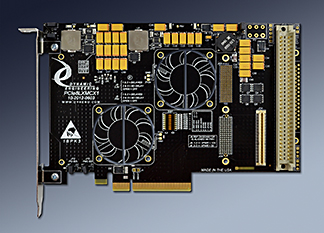

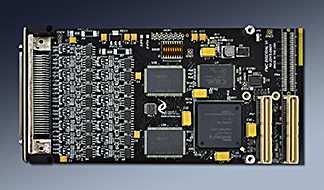

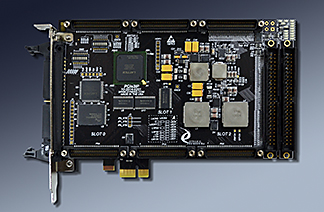

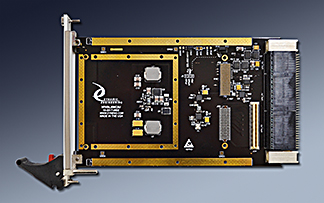

3/2025 Updated Design PCIe8LXMCX2 now features separate PCBs for SCSI and DIN versions . PCIe8LXMCX2 provides two XMC positions on a PCIe format design. Power supplies convert the system +12V to 5V, 3.3V, and -12V to support the XMC. User options to enable, disable, fast turn-on, and delayed turn-on for the 5V and 3.3V 15A supplies. Shunt selection for VPWR with 5V and 12V selections. User switch to set the global address if used. 8 PCIe lanes with matched length, impedance controlled traces to support up to Gen3 operation.

With the updated revisions the SCSI and DIN connector routing is optimized for better Rear IO performance. The -SCSI versions are built on the PCB with the SCSI optimized rear IO routing. Matched length, differential 100 ohm pairs.

Continue to order with the same part numbers. The correct PCB will automatically be selected for your project. The SCSI one for -SCSI and -NC models. [-NC can also come on the DIN version]. Both PCBs support the default, XIO, and XIOexc rear IO options. Connector Bus Option also supported on both versions

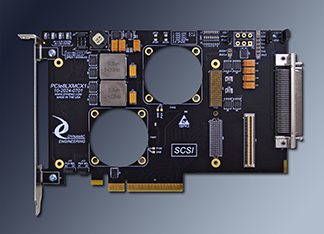

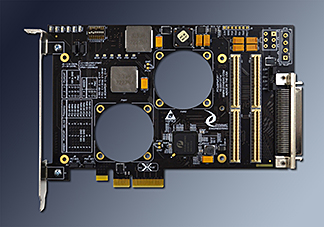

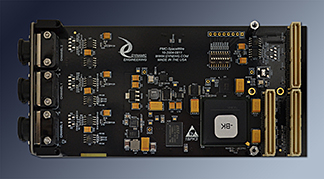

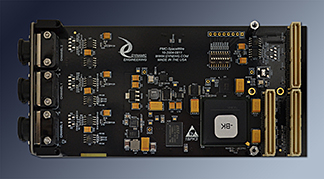

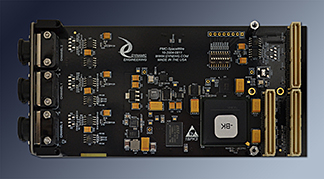

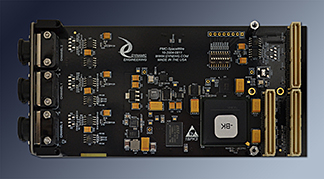

2/2025 Updated Design PCIe8LXMCX1 now features separate PCBs for SCSI and DIN versions . PCIe8LXMCX1 provides an XMC position on a PCIe format design. Power supplies convert the system +12V to 5V, 3.3V, and -12V to support the XMC. User options to enable, disable, fast turn-on, and delayed turn-on for the 5V and 3.3V 15A supplies. Shunt selection for VPWR with 5V and 12V selections. User switch to set the global address if used. 8 PCIe lanes with matched length, impedance controlled traces to support up to Gen3 operation.

With the updated revisions the SCSI and DIN connector routing is optimized for better Rear IO performance. The -SCSI versions are built on the PCB with the SCSI optimized rear IO routing. Matched length, differential 100 ohm pairs.

Continue to order with the same part numbers. The correct PCB will automatically be selected for your project. The SCSI one for -SCSI and -NC models. [-NC can also come on the DIN version]. Both PCBs support the default, XIO, and XIOexc rear IO options.

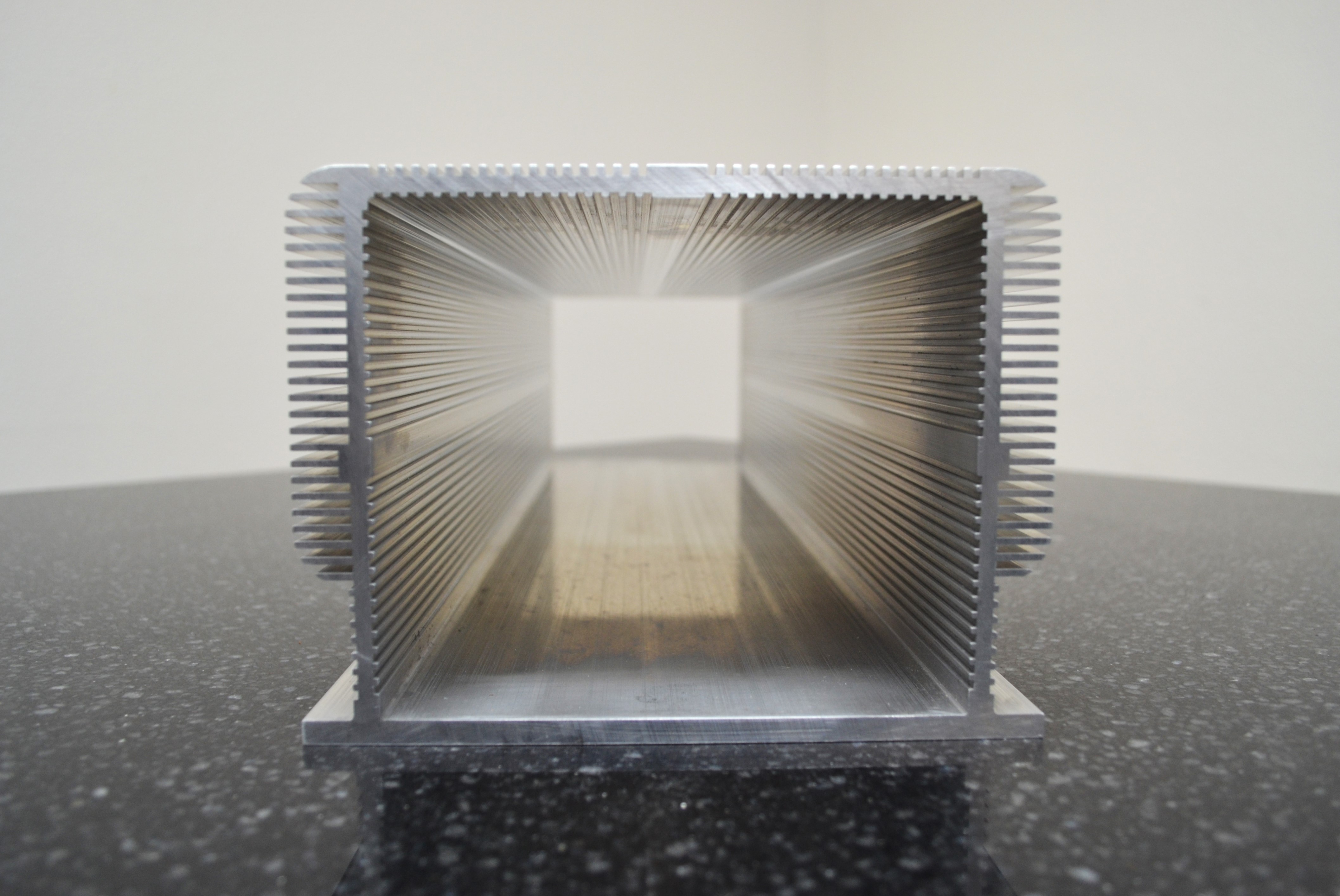

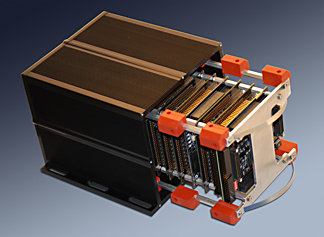

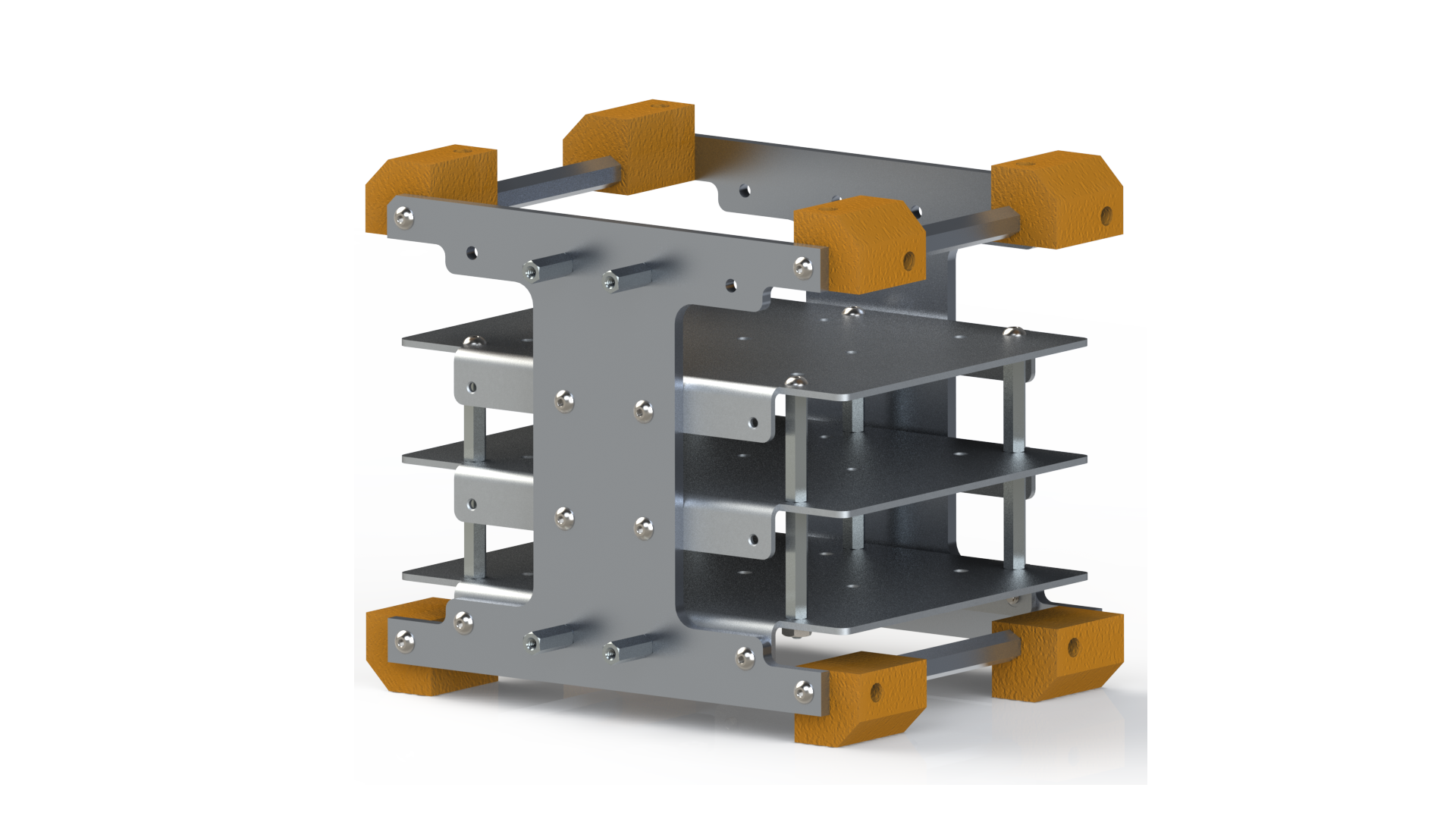

2/2025 Updated Design PC104p-Chassis Enhanced Design with expanded heat sink and new easier to use gasket design. Extrusion length is 24 inches allowing for a variety of client lengths. Standard ordering lengths in terms of PC104p modules is 1-11. Mix and match internal frame length with external chassis length for designs requiring additional non-stack hardware to be incorporated. Mechanical models are available to support your integration effort. Custom end plates to incorporate cable egress are available. Multiple finishes are available including: Raw, Anodized, Surtec and more.

Please contact Dynamic Engineering (sales@dyneng.com) for a quote of this product.

12/2024 Updated Design PCIe-Spartan-VI Windows® 10/11 package . Updated software package now supports on-the-fly programming and verification of the User FPGA under SW control. Update the BIT file in the FPGA without cables etc. Reconfigurability allows the design to be adapted to current conditions in near real time. Default programs can be programmed into the User FPGA QSPI support FLASH - for near instant on availability.

More about PCIe-Spartan-VI: User programmable Spartan VI FPGA supported with 16 DMA ports, 40 Differential IO [LVDS and or RS-485], 12 TTL, 8 PLLs with 3 clock references each. Windows SW package includes User R/W functions to control the user design plus built in features with dedicated SW. The Bus FPGA handles the host interface and provides a General Purpose 32 bit 50 MHz bus to the User FPGA plus 8 channels with Rx and Tx lanes between the Bus and User FPGAs. The lanes are byte wide and have flow control built in. SW support for DMA operation to use with the User FPGA via the byte lanes. QSPI for User image. SW based JTAG load of User FPGA in next software release. Industrial temperature components. IO supported with D100 connector. Same pinout as PCIe-AlteraCycloneIV design. Reference VHDL project available for User FPGA.

Please contact Dynamic Engineering (sales@dyneng.com) for a link to the software package. Please see the Dynamic Data Sheet for links to HW and SW manuals plus detailed information.

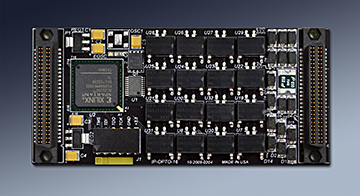

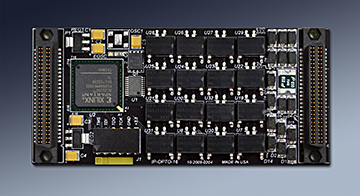

11/2024 Updated Driver and PCB Updated IO interface now uses FETs to allow up to 50V IO and up to 200 mA sink per transmit line. Each Input line now uses a series resistor and zener diode to allow a wide range - TTL - 50V on the input lines. The IP-Parallel-HV and IP-Parallel-HV-Test models have been combined. Addresses for the base model remain the same. Updated Win10 driver and reference SW package included with purchase. Test features added include controlling the second interrupt line, memory implemented in the memory space, and Address capture to support testing IP Module Carriers and developing drivers. The same PCB is utilized for IP-Parallel-HV-Miller [implements Miller encoding/decoding. Similar to Manchester], IP-HaveQuick[Time of Day receiver / transmitter utilizing HQT Manchester encoded data], and IP-Crypto[Interface with KYK-13 to read the key]. Use the manuals tab to navigate to the user manual for more detail.

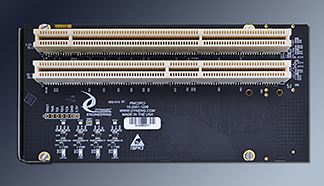

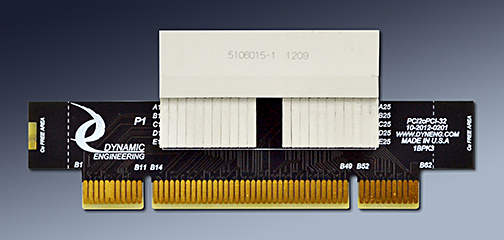

10/2024 Updated Design PMC2PCI has been updated to support continued manufacture. Passive design with 32-64 bit operation depending on carrier installed into. 25-66 MHz clock rates, 5V and 3.3V keyed slots - actual PCI voltage determined by carrier. One slot available at a time. Install a PCI device into a PMC position. Right angle mounting available for parallel PCI and PMC installation.

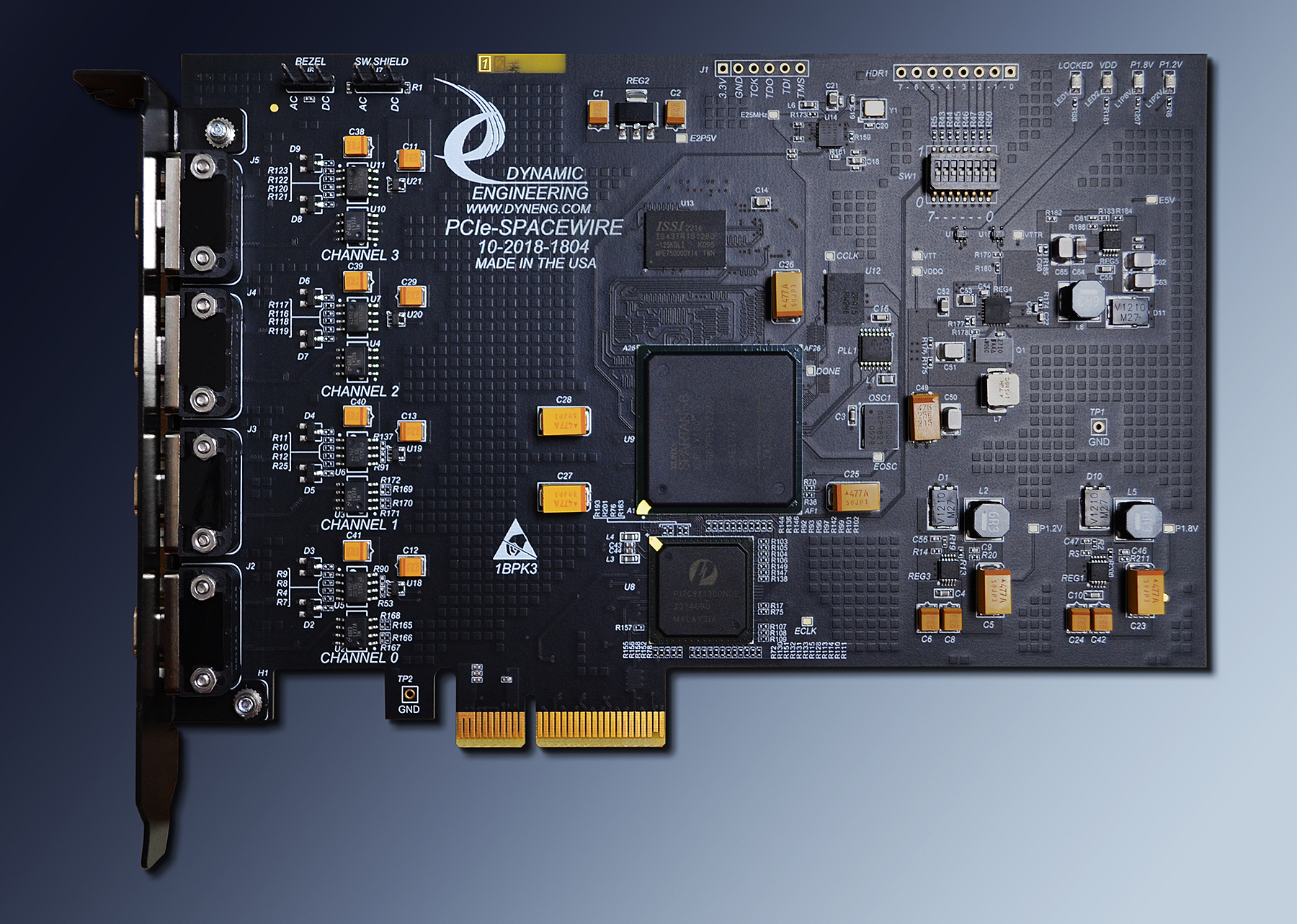

09/2024 Updated SpaceWire Monitor with more memory and two added ports by Dynamic Engineering.. SpaceWire Monitor can be used to capture the communication between two SpaceWire nodes as well as provide two standard SpaceWire nodes with all of the features of our BK models. For the monitor ports, both sides are captured, filtered and stored to memory. Data is stored by packet and each packet is pre-pended with time, number and size. SpaceWire-Monitor can capture the data needed to do system / platform validation, debug tricky communications issues, capture HW data errors and more. Software currently executes with Linux and Windows®. SpaceWire-Monitor is a build option for PCI, PCIe, PMC, PC104p, and PCI-104 models of SpaceWire IO. All models offered have 32 MegaBytes of storage per port. DMA transfers data to the user specified file. NVMe or HDD with cache recommended for file storage. Data is stored as binary. Application includes binary conversion utility to provide human readable files. Click below for the SpaceWire-Monitor data page. Use the manuals tab to navigate to the user manual for more detail.

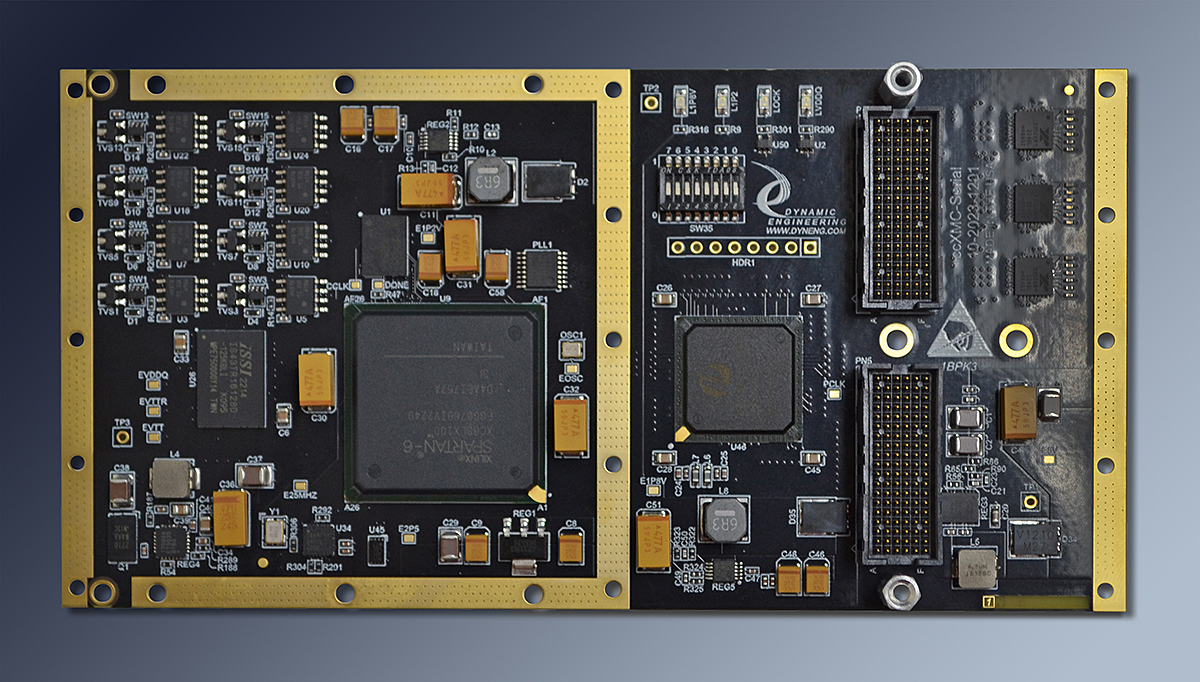

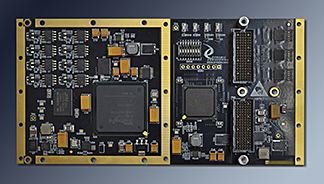

8/2024 Updated Design ccXMC-Serial has been updated with additional functionality. The new features include programmable active edge, CRC algorithm, clock count for HDLC and programmable clock burst for NRZ.. The base features include Spartan 6 FPGA, DDR, PLL, temperature sensor, 16 RS-485/LVDS transceivers, and 3 ports with programmable RS-232/RS-485 suitable for UARTs and similar. ccXMC-Serial is a conduction cooled XMC implementation. The IO is assigned to be compliant with SOSA requirements utilizing the Pn6 rear IO connector. The first design implemented on this platform is ccXMC-Serial-HDLC. 2 ports of HDLC, 2 ports of NRZL, and 3 ports of UART are implemented in this design. Windows drivers and reference SW currently available. HDLC and NRZL are supported with RS-485 transceivers.

7/2024 Updated Designs PMC-SpaceWire-BK, PCI-SpaceWire-BK , and PC104p-SpaceWire-BK PCBs and Linux packages have been updated. PMC-SpaceWire-BK, PCI-SpaceWire, and PC104p-SpaceWire join PCIe-SpaceWire-BK featuring enhanced DDR based memory with a default allocation or 32 Mbytes per port. The standard features are retained. PMC-SpaceWire-BK, PCIe-SpaceWire-BK as well as the other models implement SpaceWire [ECSS-E-ST-50-12C specification] in a convenient format. Four fully independent and highly programmable SpaceWire ports are provided by the SpaceWire-BK design. The SpaceWire protocol is advanced with link testing, error handling, command and data protocols built in. The SpaceWire electrical interface is point-to-point with token based flow control. With the SpaceWire protocol it is easy to build a heirarchical architecture system with routers or a home-run wired system. Your equipment can interact with any other node in the system. Port based DMA offloads the CPU and increases performance in your system. Time Code support provides a complete solution. Please refer to the HW manuals for detailed information. 200 MHz. Link rate, industrial temperature, DMA support, Rx ports autobaud. First character synchronization. The Win10/11 and Linux software packages support all of the features of the SpaceWire-BK design, and the UserAp reference software demonstrates the features including: internal and external loop-back with and without DMA operation. For example, several frequency files are provided and the UserAp software can automatically load them for you. Set any port to any programmable frequency. The Win10 and Linux packages are included with your purchase of SpaceWire-BK models. Please contact Dynamic Engineering (sales@dyneng.com) for a link to the software package. Please see the Dynamic Data Sheet for links to HW and SW manuals plus detailed information.

5/2024 New Design PCIe-Spartan-VI is now available. User programmable Spartan VI FPGA supported with 16 DMA ports, 40 Differential IO [LVDS and or RS-485], 12 TTL, 8 PLLs with 3 clock references each. Windows SW package includes User R/W functions to control the user design plus built in features with dedicated SW. The Bus FPGA handles the host interface and provides a General Purpose 32 bit 50 MHz bus to the User FPGA plus 8 channels with Rx and Tx lanes between the Bus and User FPGAs. The lanes are byte wide and have flow control built in. SW support for DMA operation to use with the User FPGA via the byte lanes. QSPI for User image. SW based JTAG load of User FPGA in next software release. Industrial temperature components. IO supported with D100 connector. Same pinout as PCIe-AlteraCycloneIV design. Reference VHDL project available for User FPGA.

Please contact Dynamic Engineering (sales@dyneng.com) for a link to the software package. Please see the Dynamic Data Sheet for links to HW and SW manuals plus detailed information.

5/2024 New Design ccXMC-Serial is now available. The base features include Spartan 6 FPGA, DDR, PLL, temperature sensor, 16 RS-485/LVDS transceivers, and 3 ports with programmable RS-232/RS-485 suitable for UARTs and similar. ccXMC-Serial is a conduction cooled XMC implementation. The IO is assigned to be compliant with SOSA utilizing the Pn6 rear IO connector. The first design implemented on this platform is ccXMC-Serial-HDLC. 2 ports of HDLC, 2 ports of NRZL, and 3 ports of UART are implemented in this design. Windows drivers and reference SW currently available. HDLC and NRZL are supported with RS-485 transceivers.

3/2024 Updated Design PCIe-SpaceWire-BK PCB and Windows package Has been updated. Now featuring enhanced DDR based memory with a default allocation or 32 Mbytes per port. The standard features are retained. PCIe-SpaceWire-BK as well as the other models implement SpaceWire [ECSS-E-ST-50-12C specification] in a convenient format. Four fully independent and highly programmable SpaceWire ports are provided by the SpaceWire-BK design. The SpaceWire protocol is advanced with link testing, error handling, command and data protocols built in. The SpaceWire electrical interface is point-to-point with token based flow control. With the SpaceWire protocol it is easy to build a heirarchical architecture system with routers or a home-run wired system. Your equipment can interact with any other node in the system. Port based DMA offloads the CPU and increases performance in your system. Time Code support provides a complete solution. Please refer to the HW manuals for detailed information. 200 MHz. Link rate, industrial temperature, DMA support, Rx ports autobaud. First character synchronization. The Win10/11 software package supports all of the features of the SpaceWire-BK design, and the UserAp reference software demonstrates the features including: internal and external loop-back with and without DMA operation. For example, several frequency files are provided and the UserAp software can automatically load them for you. Set any port to any programmable frequency. The Win10 package is included with your purchase of SpaceWire-BK models. Please contact Dynamic Engineering (sales@dyneng.com) for a link to the software package. Please see the Dynamic Data Sheet for links to HW and SW manuals plus detailed information.

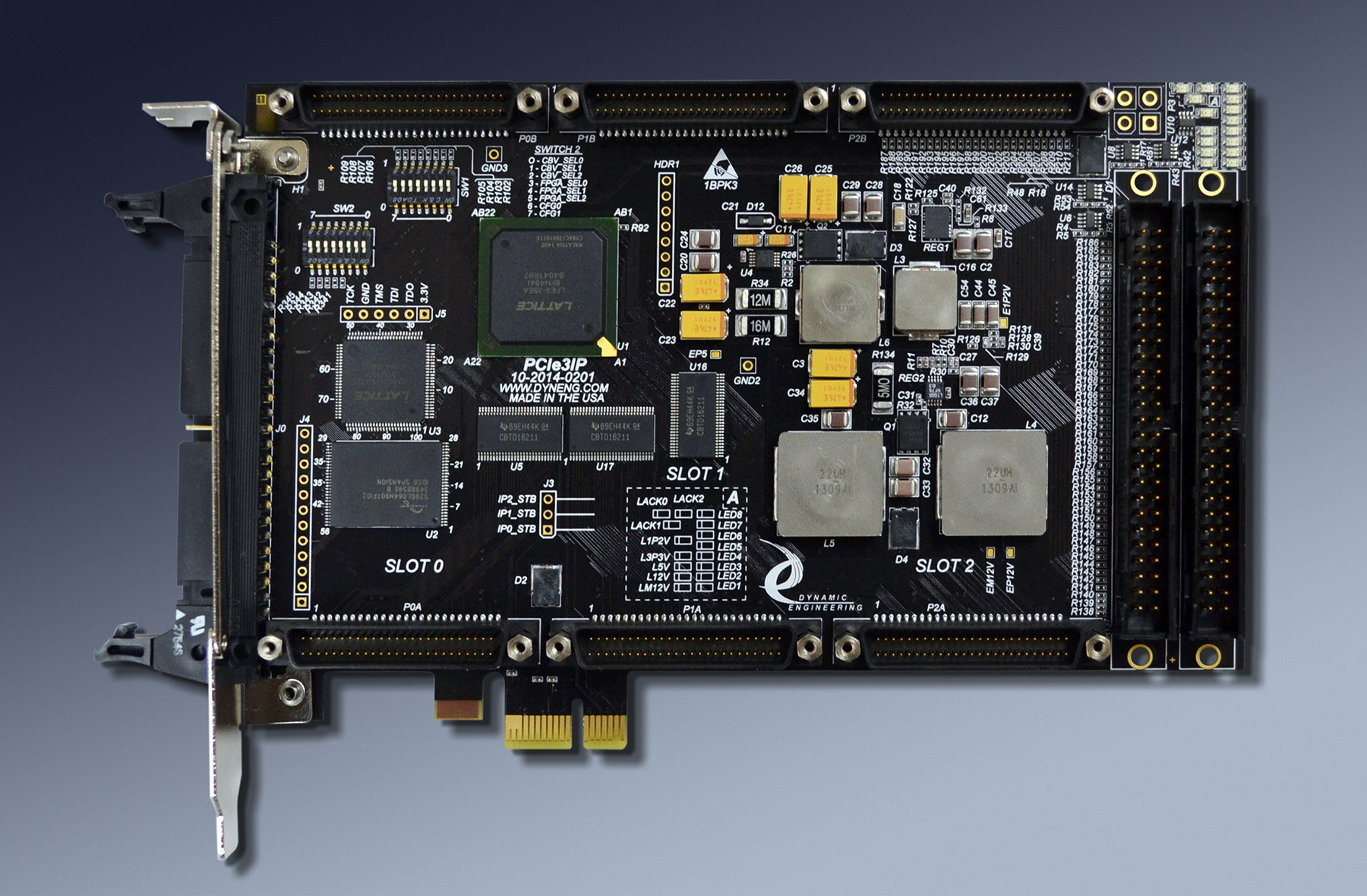

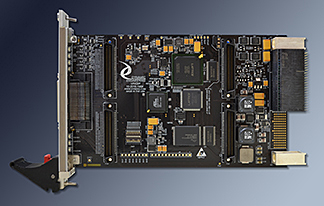

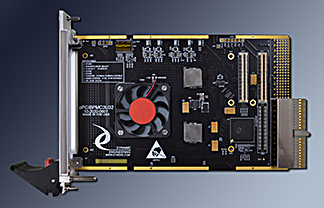

2/2024 Updated Design PCIeBPMCX1 Has been updated. The bridge in use since 2007 went EOL and has been replaced with a Pericom PI7C9X130DNDE. The new bridge retains the 1-4 lane PCIe capability and provides the same options for 32/64 bits and 25-133 MHz. Please see the updated manual for settings and more detailed descriptions. In addition the 5V and 3.3V power supplies have been updated to provide up to 15A each. A new feature is an optional AP power connector with a standard 2x3 configuration to match PC internal power harnesses. The rear IO and bezel IO configurations are retained to provide a constant interface for cabling. The bridge is transparent and no SW changes required unless optimizing for high speed DMA operation. Please see the Dynamic Data Sheet for links to HW manuals and detailed information.

8/2023 Updated Design VPX-GLIB Has been updated to incorporate the PCIe interface to operate in parallel with the original SPI control path. VPX-GLIB is a multi-purpose hardware design supplying many system supervisor and space saving interfaces. VPX-GLIB is controlled via SPI bus [LVDS] using CLK, EN, SEL [2-0], MOSI, MISO. The SPI interface with the CPU is received and decoded. SPI accesses to internal functions are re-routed to a second decoder which extracts data to be written or packages data to be read. The extracted data is stored into a local register, and then parallel loaded to the target register. Accesses for SMB are re-routed to that interface. The PCie interface operates in parallel with the SPI interface - both affect the same register set allowing for either or both buses to be used for control. Base design provides LVDS, 485, single ended electrical interfaces with conversion, direction and termination control. Local voltage plus external voltage measurements with 3x LM81s, remote temperature measurement [TMP422] with automated HW interface, Multi-voltage inputs with programmable set-points. 10 MHz Clock reference testing and forwarding. Industrial Temperature range. Please see the Dynamic Data Sheet for links to HW manuals and detailed information. Win10 software package available to support access over the PCIe bus.

8/2023 New Design PCIe8LXMCX2HL A customized version of PCIe8LXMCX2. The rear IO options are optimized for the client requirement with the XMC rear IO broken out to 4 connectors per position. The interconnects are a combination of 50 ohm single ended and 150 ohm differential pairs. The differential signals are matched length. Base features common with PCIe8LXMCX2: Adapt 1 or 2 XMCs into a PCIe system. Gen1-3 compatible, Updated switch, clock distribution, incorporated Connector Bus, and power supplies. 8 lane connection to the PCIe bus with 8 PCIe lanes to each of the XMC positions. Options for FANs, and added external power. Bezel IO also supported. Internal Power Supplies for +5V, 3.3V, and -12V. +12V routed from PCIe interface.

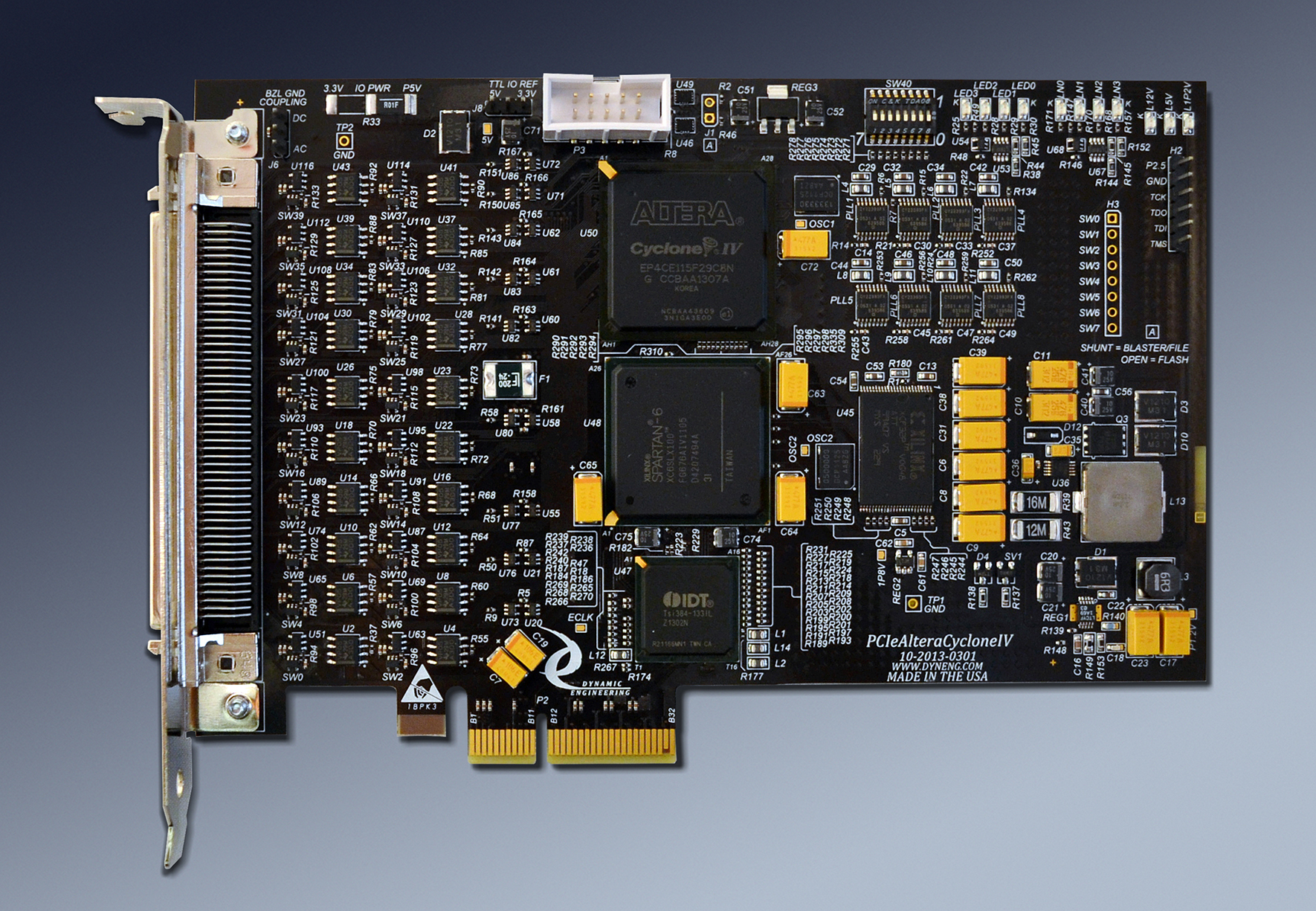

8/2023 Updated Windows Package PCIeAlteraCycloneIV is now supported with Win10/11 drivers and reference SW. Driver and Hardware Manuals are available for download. Both drivers [Linux and Windows] are available to clients of PCIeAlteraCycloneIV along with reference software showing how to use the software to control the User design. Support package includes generic Read and Write operations to support user changes to the base memory map.

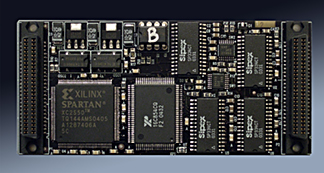

PCIeAlteraCycloneIV features Cyclone IV FPGA - 115, GPIO control bus plus 16 DMA channels to support user designs based on RS-485 and / or LVDS IO types. A Spartan 6 FPGA handles the traffic in and out of the PCIe bus and the user has access to the Cyclone IV. 40 differential pairs and 12 TTL IO are available to the user along with 24 PLLs.

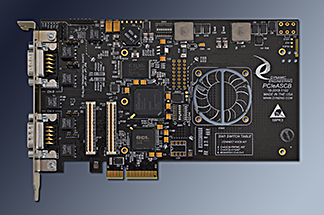

07/2023 Updated ASCB interface for PCIe. Due to parts shortages ASCB has been redesigned to provide greater availability. ASCB is supported with two dual redundant ports utilizing the standard DB9 connector and pinout. D [Manchester] and Enhanced [8b10b] protocols supported. Dual Port RAM is used to store messages to transmit and data received from the ASCB interface. DMA is supported. In addition, a PMC position is supplied to support applications with need of local processing in the form of a PrPMC. Alternatively the PMC position can be used to add more IO to your system. Windows® SW package by Dynamic Engineering. Linux package by The Goebel Company.

06/2023 New SpaceWire Monitor Windows® SW package by Dynamic Engineering. SpaceWire Monitor can be used to capture the communication between two SpaceWire nodes. Both sides are captured, filtered and stored to memory. Data is stored by packet and each packet is pre-pended with time, number and size. SpaceWire-Monitor can capture the data needed to do system / platform validation, debug tricky communications issues, capture HW data errors and more. Software currently executes with Linux and Windows®. SpaceWire-Monitor is a build option for PCI, PCIe, PMC, PC104p, and PCI-104 models of SpaceWire IO. All models offered have 576 KBytes of storage per port. DMA transfers data to the user specified file. NVMe or HDD with cache recommended for file storage. Data is stored as binary. Application includes binary conversion utility to provide human readable files. Click below for the SpaceWire-Monitor data page. Use the manuals tab to navigate to the user manual for more detail.

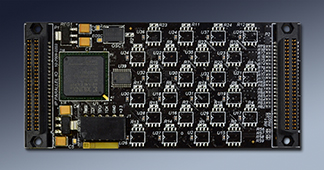

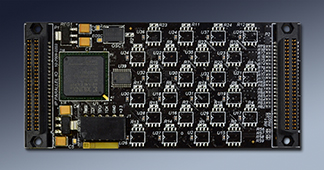

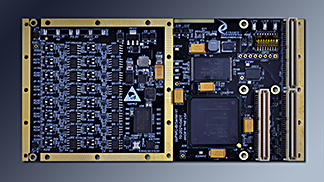

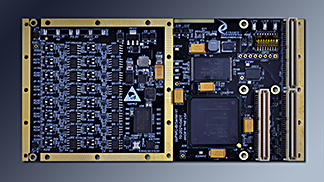

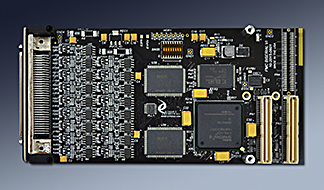

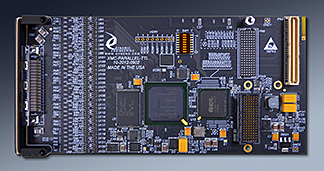

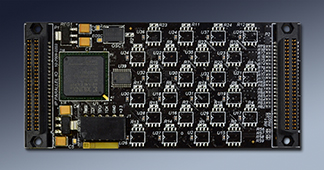

4/2023 Linux Support Package for PMC-Parallel-485-NG1.

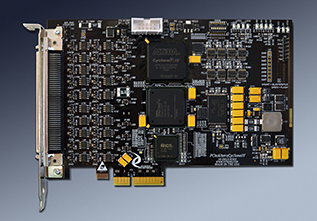

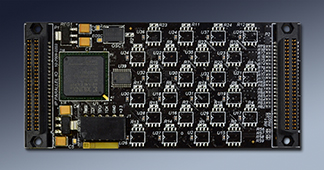

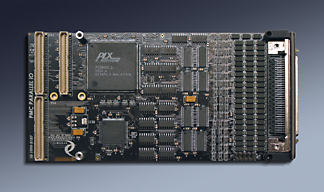

PMC-Parallel-485-NG1 provides register based GPIO plus 2 cascaded counters, fused 3.3V, received and redriven differential pair. The counters can be operated with a divided clock with external and internal sources. The counters can be used as interrupt generators. Total count or specific bits within the count can be selected. The base design has 32 + 2 RS-485/RS-422 or LVDS. Programmable Tx/Rx and termination. Programmable interrupt / polled IO with rising, falling, level, inversion options per bit. Separate mask to allow combination of polled and interrupt driven IO. 2 additional IO at bezel for external clock and clock enable. Industrial Temperature components. Linux package supports all modes and comes with reference SW and test menu - included with purchase of PMC-Parallel-485-NG1. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab. Windows and Linux currently supported.

2/2023 Win 10/11 Driver IP-1553 now features a Window® support package. The hardware includes a Spartan VI FPGA and HOLT 1553 interface. These updates provide Mil-STD-1553 support in an IndustryPack format. Industrial temperature components throughout. SW compatible with the previous versions. Win10 and Linux SW packages. Control all aspects of the single (-1) or two port (-2) models. Each port is dual redundant with header options for direct and transformer coupled operation. IP-1553 Windows module driver is used with Dynamic Engineering IndustryPack carriers/drivers. For use with PCIe3IP, PCIe5IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP, PC104p4IP

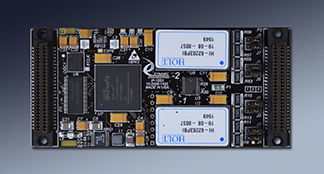

1/2023 Maxwell-2 Revision 02 released.

Maxwell-2 is a standalone micro computer with FPGA, Memory, CPU and IO. Spartan 6 [45 or 75] with QSPI FLASH to configure. Micro Blaze CPU built into the FPGA fabric allowing embedded Linux applications to run along with custom VHDL/Verilog implementations for your project. DDR, FRAM, FLASH, Ethernet, USB, Parallel Ports, LEDs, RTC with battery back-up, plus push button and dipswitches for user input. Internal power supplies only require a 5V external input. Multiple clock references supplied to FPGA and IO devices. Industrial Temperature components. Reference manual available on the Dynamic Data Sheet. See the Models tab.

12/2022 Win10/11 Support Package for PMC-Parallel-485-NG1.

PMC-Parallel-485-NG1 provides register based GPIO plus 2 cascaded counters, fused 3.3V, received and redriven differential pair. The counters can be operated with a divided clock with external and internal sources. The counters can be used as interrupt generators. Total count or specific bits within the count can be selected. The base design has 32 + 2 RS-485/RS-422 or LVDS. Programmable Tx/Rx and termination. Programmable interrupt / polled IO with rising, falling, level, inversion options per bit. Separate mask to allow combination of polled and interrupt driven IO. 2 additional IO at bezel for external clock and clock enable. Industrial Temperature components. Windows package supports all modes and comes with reference SW and test menu - included with purchase of PMC-Parallel-485-NG1. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab. Linux for this model is scheduled.

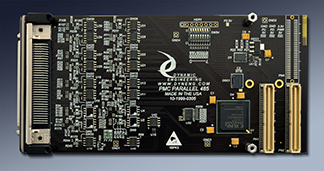

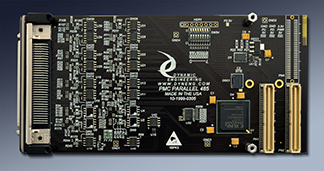

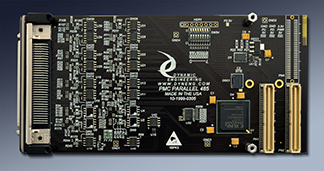

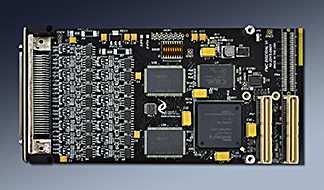

08/2022 Win10 Support Package for PMC-Parallel-485.

Register based GPIO with options for bezel and rear panel IO. 32 + 2 RS-485/RS-422 or LVDS. Programmable Tx/Rx and termination. Programmable interrupt / polled IO with rising, falling, level, inversion options per bit. Separate mask to allow combination of polled and interrupt driven IO. 2 additional IO at bezel for external clock and clock enable. Industrial Temperature components. Windows package supports all modes and comes with reference SW and test menu - included with purchase of PMC-Parallel-485. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

Register based GPIO with options for bezel and rear panel IO. 32 + 2 RS-485/RS-422 or LVDS. Programmable Tx/Rx and termination. Programmable interrupt / polled IO with rising, falling, level, inversion options per bit. Separate mask to allow combination of polled and interrupt driven IO. 2 additional IO at bezel for external clock and clock enable. Industrial Temperature components. Windows package supports all modes and comes with reference SW and test menu - included with purchase of PMC-Parallel-485. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.11/22 Updated Design: PCIe8LXMCX2 Adapt 1 or 2 XMCs into a PCIe system with PCIe8LXMCX2. Now Gen1-3 compatible, Updated switch, clock distribution, incorporated Connector Bus, and power supplies. 8 lane connection to the PCIe bus with 8 PCIe lanes to each of the XMC positions. Connector Bus option creates a high speed inter-connect between the XMC rear IO connectors to support Signal Processing and other high bandwidth requirements. Isolation resistors are incorporated for almost zero stub length. Matched length for each option, impedance controlled, differential routing. Standard differential pair definitions. Options for Jn4, Jn6, FANs, rear IO connector types, and added external power. Bezel IO also supported. Internal Power Supplies for +5V, 3.3V, and -12V. +12V routed from PCIe interface. A detailed selection map is available in the manual. See Dynamic Data Sheet for more information and manuals.

11/2022 New Version IP-Parallel-TTL-PATT features a 32 bit Pattern Generator plus 16 bit GPIO port [TTL / LVTTL interface]. 100 MHz reference along with user programmed divisors to supply COS and Pattern Generation references. Pattern Generator currently has 8 Types to choose from. The first option is User Data. Patterns written to the FIFO [4Kx32] are broadcast at the programmed rate. The remaining types utilize the built in controller to output the selected pattern. The limits [Start and Stop], Rate of Change [Slope], Number of cycles to output [Count], and Horizontal Count [HCount] are used to control the operation of Rising and Falling Ramps, Pyramids and inverted Pyramids, Square Wave, Shift Up, and Trapezoidal waveforms. Various status and optional interrupts are available to manage the interface. The recieve mode can be enabled to operate separately or in parallerl with the Pattern Generator. Data is captured on the rising edge of the reference clock and stored into the Rx FIFO [4Kx32]. Driver has Read and Write File operations for burst reads and writes when using the FIFOs.

In addition, a 16 bit GPIO parallel port with COS [change of state] capability is provided. Selectable Rising, Falling, Interrupt Enable, Polariity, Direction, Edge/Level controls to provide complete control over the interface. Win10/11 support. .

10/2022 New Version IP-Parallel-TTL-DPR provides a parallel interface to interconnect with a memory based system. A19-0, D15-0, READ, WRITE, ACK, BUSY supported. 100 MHz reference used to have precise timing. Simple structure to send commands to the interface to Write to memory, Read from memory and Read multiple from memory. Commands stored in 255 deep FIFO queue. 1Kx16 FIFO to store data from Read commands. In addition, an 8 bit GPIO parallel port with COS [change of state] capability is provided. Programmable sample rate for COS operation. Win10/11 support. Target simulator developed for test purposes. If your timing is different let us know know and we can modify to suit your requirements..

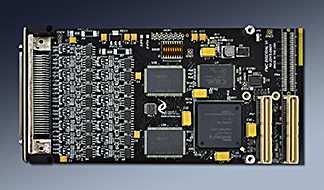

09/2022 Updated Model "ORN1" of ccPMC-BiSerial-VI.

2 ports with SDLC and 2 ports with NRZ/NRZL functions. Parallel port with mux control to select SDLC, NRZ/NRZL, or Parallel port operation. SDLC is Dual Port RAM based with programmable message length, interrupts etc. NRZ/NRZL is highly configurable with number of bits per transfer [packet descriptors], MSB/LSB first operation, Clock Sense, Data Sense, frequency of transmission, time between packets sent, time to wait for end of message, Programmable flags for Almost Full and Almost Empty FIFO. Interrupt or polled operation. 32 differential IO [485 or LVDS]. Temperature Sensor with state-machine to manage serial interface. PLL for custom frequencies. Industrial Temperature components. Rear IO (Pn4). Windows package supports all modes and comes with reference SW and test menu. VxWorks package - 6.9 supported. Linux package released. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

2 ports with SDLC and 2 ports with NRZ/NRZL functions. Parallel port with mux control to select SDLC, NRZ/NRZL, or Parallel port operation. SDLC is Dual Port RAM based with programmable message length, interrupts etc. NRZ/NRZL is highly configurable with number of bits per transfer [packet descriptors], MSB/LSB first operation, Clock Sense, Data Sense, frequency of transmission, time between packets sent, time to wait for end of message, Programmable flags for Almost Full and Almost Empty FIFO. Interrupt or polled operation. 32 differential IO [485 or LVDS]. Temperature Sensor with state-machine to manage serial interface. PLL for custom frequencies. Industrial Temperature components. Rear IO (Pn4). Windows package supports all modes and comes with reference SW and test menu. VxWorks package - 6.9 supported. Linux package released. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.09/2022 Win10 Support Package for PMC-Parallel-485.

New Feature included in support package. Two new utilities are available on the UserAp menu: Print Registers and Modify Registers. Print Registers reads and prints the current contents of the registers within PMC-Parallel-485. Registers supported with structures have the settings displayed showing the current values of the structure. Modify Registers allows the user to change the settings on the board without writing software. Quick start options to program to transmit or receive. Toggle option to have a register change between two values via single key stroke. Great for initial familiarization and to use PMC-Parallel-485 as a tool to interact with other hardware. The rest of the files within UserAp provide a great references for initialization - connecting with the driver, performing IO tests, using interrupts, and more.

New Feature included in support package. Two new utilities are available on the UserAp menu: Print Registers and Modify Registers. Print Registers reads and prints the current contents of the registers within PMC-Parallel-485. Registers supported with structures have the settings displayed showing the current values of the structure. Modify Registers allows the user to change the settings on the board without writing software. Quick start options to program to transmit or receive. Toggle option to have a register change between two values via single key stroke. Great for initial familiarization and to use PMC-Parallel-485 as a tool to interact with other hardware. The rest of the files within UserAp provide a great references for initialization - connecting with the driver, performing IO tests, using interrupts, and more.PMC-Parallel-485 provides register based GPIO with options for bezel and rear panel IO. 32 + 2 RS-485/RS-422 or LVDS. Programmable Tx/Rx and termination. Programmable interrupt / polled IO with rising, falling, level, inversion options per bit. Separate mask to allow combination of polled and interrupt driven IO. 2 additional IO at bezel for external clock and clock enable. Industrial Temperature components. Windows package supports all modes and comes with reference SW and test menu - included with purchase of PMC-Parallel-485. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

08/2022 Win10 Support Package for PMC-Parallel-485.

Register based GPIO with options for bezel and rear panel IO. 32 + 2 RS-485/RS-422 or LVDS. Programmable Tx/Rx and termination. Programmable interrupt / polled IO with rising, falling, level, inversion options per bit. Separate mask to allow combination of polled and interrupt driven IO. 2 additional IO at bezel for external clock and clock enable. Industrial Temperature components. Windows package supports all modes and comes with reference SW and test menu - included with purchase of PMC-Parallel-485. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

Register based GPIO with options for bezel and rear panel IO. 32 + 2 RS-485/RS-422 or LVDS. Programmable Tx/Rx and termination. Programmable interrupt / polled IO with rising, falling, level, inversion options per bit. Separate mask to allow combination of polled and interrupt driven IO. 2 additional IO at bezel for external clock and clock enable. Industrial Temperature components. Windows package supports all modes and comes with reference SW and test menu - included with purchase of PMC-Parallel-485. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.08/2022 New Model "ORN1" of ccPMC-BiSerial-VI.

2 ports with SDLC and 2 ports with NRZ/NRZL functions. Parallel port with mux control to select SDLC, NRZ/NRZL, or Parallel port operation. SDLC is Dual Port RAM based with programmable message length, interrupts etc. NRZ/NRZL is highly configurable with number of bits per transfer [packet descriptors], MSB/LSB first operation, Clock Sense, Data Sense, frequency of transmission, time between packets sent, time to wait for end of message, Programmable flags for Almost Full and Almost Empty FIFO. Interrupt or polled operation. 32 differential IO [485 or LVDS]. Temperature Sensor with state-machine to manage serial interface. PLL for custom frequencies. Industrial Temperature components. Rear IO (Pn4). Windows package supports all modes and comes with reference SW and test menu. VxWorks is released - 6.9 supported. Linux in process. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

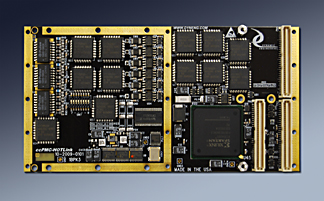

2 ports with SDLC and 2 ports with NRZ/NRZL functions. Parallel port with mux control to select SDLC, NRZ/NRZL, or Parallel port operation. SDLC is Dual Port RAM based with programmable message length, interrupts etc. NRZ/NRZL is highly configurable with number of bits per transfer [packet descriptors], MSB/LSB first operation, Clock Sense, Data Sense, frequency of transmission, time between packets sent, time to wait for end of message, Programmable flags for Almost Full and Almost Empty FIFO. Interrupt or polled operation. 32 differential IO [485 or LVDS]. Temperature Sensor with state-machine to manage serial interface. PLL for custom frequencies. Industrial Temperature components. Rear IO (Pn4). Windows package supports all modes and comes with reference SW and test menu. VxWorks is released - 6.9 supported. Linux in process. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.5/2022 New Version: PCIe4LHOTLinkx5-SMB HOTLink is used in applications demanding high speed and high reliability including photography, sonar, radar, other scanning applications, seismic, oil exploration etc. Alternate purposes would include high speed buses between equipment or within equipment for command and control, data transfer etc. PCIe4LHOTLinkx5 is a PCI Express device. The -SMB version has a single channel with Tx and Rx ports utilizing the SMB connectors. The HOTLink ports are supported with separate DMA transfer engines plus local memory. Full duplex operation with 256Kbytes of FIFO memory per port. The standard version has many triggering / transfer control programmable features to allow start of frame sequences, end of frame sequences, synchronized start across channels, constant [programmed] delay between frames. Win10 driver and reference application available. See Dynamic Data Sheet for more information and manuals.

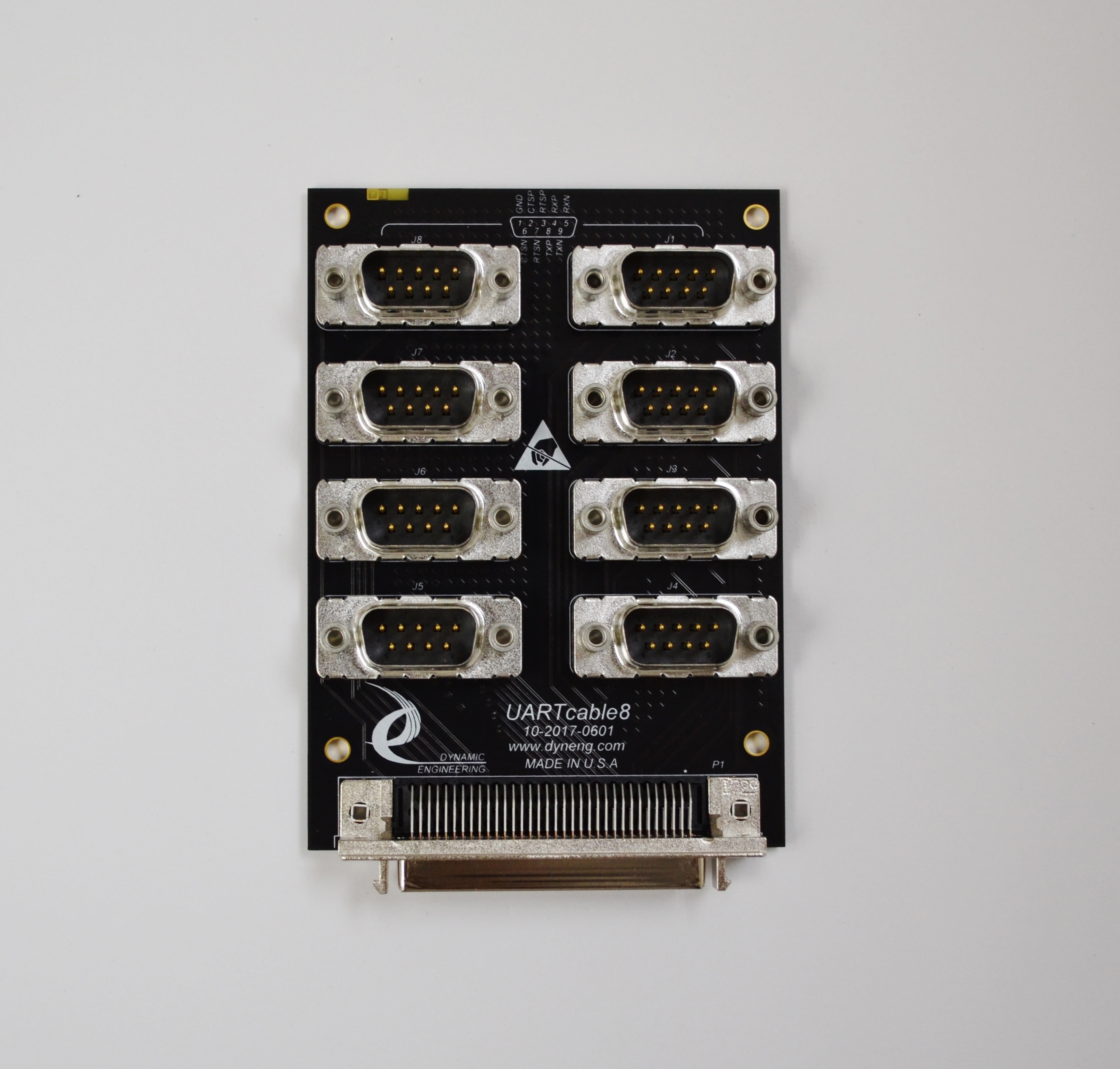

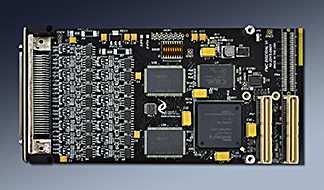

05/2022 PMC-OctalUART-232 Win10 - Dynamic Engineering has updated the software package for PMC-OctalUART-232 with Windows 10 support. The SW package is included with your purchase of PMC-OctalUART-232. Drivers and UserAp reference package with examples for set-up [baud rate, word size, stop bits, RTS/CTS etc.], Transmitting and Receiving characters. Internal and External loop-back examples. External tests with and without flow control in use. Driver includes IOCTLs for write multiple and read multiple. Signals [RX, TX, RTS, CTS, DTR, DSR per port]. Eight ports per device. ROHS or standard processing. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information. Rear IO model shown below.

04/2022 IP-QuadUART-485 Win10 - Dynamic Engineering has updated the software package for IP-QuadUART-485 with Windows 10 support. The SW package is included with your purchase of IP-QuadUART-485. Drivers and UserAp reference package with examples for set-up [baud rate, word size, stop bits, RTS/CTS etc.], Selection of Full or half duplex RS-485 operation, Transmitting and Receiving characters. Internal and External loop-back examples. External tests with and without flow control in use. Driver includes IOCTLs for write multiple and read multiple. 485 signals [RX, TX, RTS, CTS, DTR, DSR per port]. Four ports per device. Designed to work with Dynamic Engineering IP Carrier group driver package. ROHS or standard processing. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information.

04/2022 IP-QuadUART Win10 - Dynamic Engineering has updated the software package for IP-QuadUART with Windows 10 support. The SW package is included with your purchase of IP-QuadUART. Drivers and UserAp reference package with examples for set-up [baud rate, word size, stop bits, RTS/CTS etc.], Selection of RS-232 or RS-485 operation, Transmitting and Receiving characters. Internal and External loop-back examples. External tests with and without flow control in use. Driver includes IOCTLs for write multiple and read multiple. 485 signals [RX, TX, RTS, CTS per port] 232 signals[Rx, Tx, RTS, CTS, DTR, DSR, RI, CD per port]. Four ports per device. Designed to work with Dynamic Engineering IP Carrier group driver package. ROHS or standard processing. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information.

04/2022 PC104p-SpaceWire updated - Dynamic Engineering has updated PC104p-SpaceWire to support the BK and SpaceWire Monitor models. Purchase includes Win10 and Linux SW support. 4 ports each separately programmable to operate up to 200 MHz. DMA engine for each port / direction [8 total]. Time code included. Standard MDM connectors. RMAP with separate Linux package. Industrial temperature components standard. Options for added memory [see -128 models], ROHS or standard processing. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information.

03/2022 VPX2IP updated - Dynamic Engineering has updated VPX2IP to have Win10 support along with more clocking options and VHDCI connectors at the bezel / front panel. VPX2IP is a 3U 4HP mechanical configuration with two IP Module locations. Front Panel IO is standard utilizing two 68 position VHDCI connectors at the VPX bezel. Compatible with standard VHDCI cable. VHDCIterm68 can be used as a breakout. Rear Panel IO is also available with IP module IO routed to the VPX rear connector [P2/J2]. Multi-word transfers are supported: 64, 32, 16, and 8 bit transfers are easy to implement with standard CPUs. VPX2IP has built in power supplies with fused filtered power to the IP positions, independent IP buses, Industrial Temperature range components, Independent 8 and 32 MHz IP Module operation. The independent IP module buses allow for parallel processing of IP accesses for higher performance. PCIe single lane operation. Windows, Linux, and VxWorks drivers and reference software. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information.

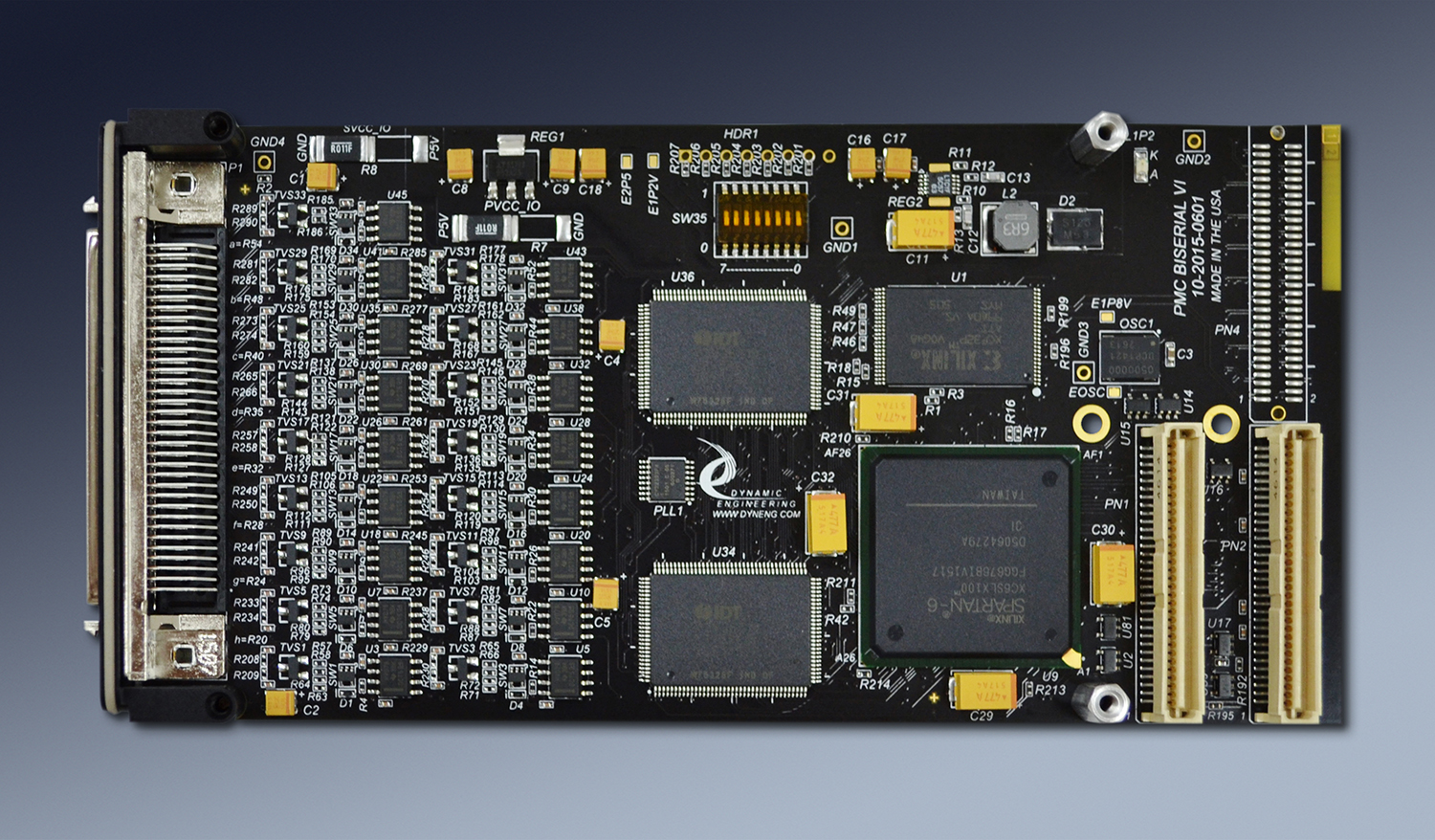

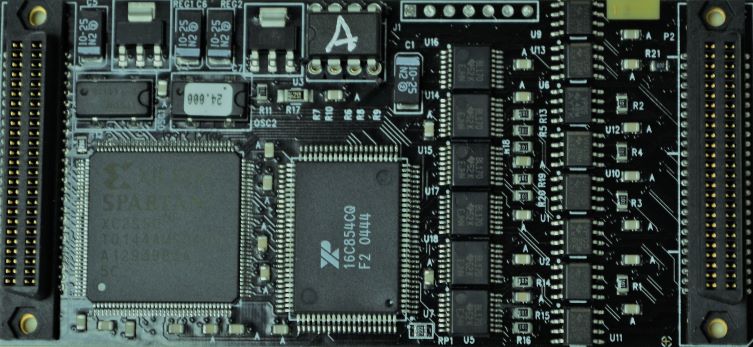

12/2021 Option for alternate pinout of PMC-BiSerial-VI-UART.

The -LM12 option selects an alternate FLASH installation with pinouts matching the Abaco / Radstone PMC-Q1F design. PMC-BiSerial-VI-UART-LM12 features the same design just rearranged. The extra features from the standard -UART design are pushed onto unused pins. 8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. Alternate reference frequencies are available. Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.

Windows and Linux packages support all modes and comes with reference SW. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

The -LM12 option selects an alternate FLASH installation with pinouts matching the Abaco / Radstone PMC-Q1F design. PMC-BiSerial-VI-UART-LM12 features the same design just rearranged. The extra features from the standard -UART design are pushed onto unused pins. 8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. Alternate reference frequencies are available. Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.

Windows and Linux packages support all modes and comes with reference SW. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.12/2021 Updated SpaceWire Software Release Dynamic Engineering has released revision 1p5 of the Windows 10 support package for SpaceWire-BK models. All types including curent releases of PMC, PCI, PCI-104, PCIe can use the updated package.

PCIe-SpaceWire-BK as well as the other models implement SpaceWire [ECSS-E-ST-50-12C specification] in a convenient format. Four fully independent and highly programmable SpaceWire ports are provided by the SpaceWire-BK design. The SpaceWire protocol is advanced with link testing, error handling, command and data protocols built in. The SpaceWire electrical interface is point-to-point with token based flow control. With the SpaceWire protocol it is easy to build a heirarchical architecture system with routers or a home-run wired system. Your equipment can interact with any other node in the system. Port based DMA offloads the CPU and increases performance in your system. Time Code support provides a complete solution. Please refer to the HW manuals for detailed information. 200 MHz. Link rate, industrial temperature, DMA support, Rx ports autobaud. First character synchronization. The Win10 software package supports all of the features of the SpaceWire-BK design, and the UserAp reference software demonstrates the features including: internal and external loop-back with and without DMA operation. For example, several frequency files are provided and the UserAp software can automatically load them for you. Set any port to any programmable frequency. The Win10 package is included with your purchase of SpaceWire-BK models. Please contact Dynamic Engineering (sales@dyneng.com) for a link to the software package.

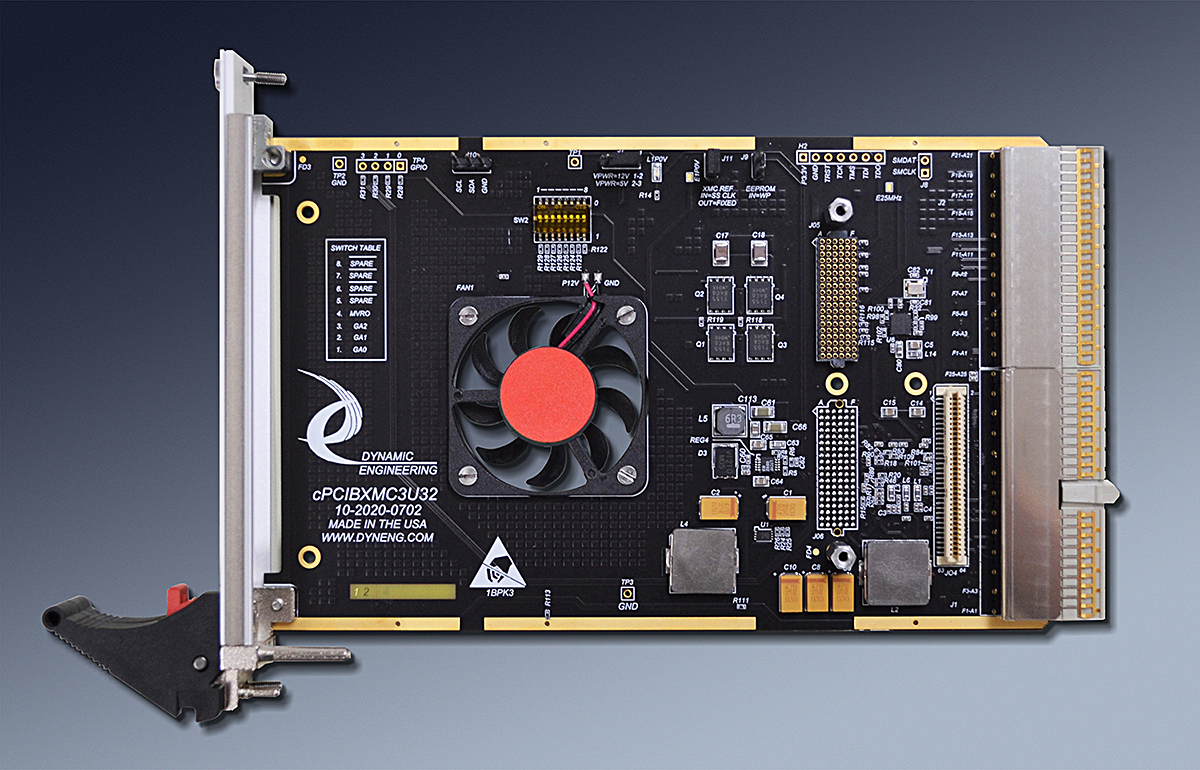

11/2021 New Design cPCIBPMC3U32.

3U 4HP cPCI adapter for PMC. Transparent bridged model with 5V / 3.3V compatible PCI interface on primary side and selctable voltage on secondary [PMC] side of bridge. 32 bit plug and play PCI operation. 33/66 MHz primary. Up to the primary frequency for secondary clock. PMC IO through the bezel. Option for rear IO using Pn4/Jn4 routed to cPCI J2. Matched length, impedance controlled [100 ohm differential] for rear IO. Local filtering on 3.3V and 5V power rails with full current mini-planes to power the PMC. +/- 12V also supplied with 1A+ traces. Industrial temperature. Fan option. ROHS option. Conformal Coating option. Isolate by voltage or clock rate. PCI trace lengths are within specification. Reference manual available on the Dynamic Data Sheet. See the Manuals tab.

3U 4HP cPCI adapter for PMC. Transparent bridged model with 5V / 3.3V compatible PCI interface on primary side and selctable voltage on secondary [PMC] side of bridge. 32 bit plug and play PCI operation. 33/66 MHz primary. Up to the primary frequency for secondary clock. PMC IO through the bezel. Option for rear IO using Pn4/Jn4 routed to cPCI J2. Matched length, impedance controlled [100 ohm differential] for rear IO. Local filtering on 3.3V and 5V power rails with full current mini-planes to power the PMC. +/- 12V also supplied with 1A+ traces. Industrial temperature. Fan option. ROHS option. Conformal Coating option. Isolate by voltage or clock rate. PCI trace lengths are within specification. Reference manual available on the Dynamic Data Sheet. See the Manuals tab.11/2021 New Design GPIO model of ccPMC-BiSerial-VI.

32 differential IO [485 or LVDS]. Each IO is independent with programming options for Edge or Level, COS (Change of State), Interrupt, Polarity. Programmable PLL plus on-board oscillator with secondary divider to supply COS reference frequency. Temperature Sensor with state-machine to manage serial interface. Industrial Temperature components. Rear IO (Pn4). Windows package supports all modes and comes with reference SW and test menu. Linux scheduled. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

32 differential IO [485 or LVDS]. Each IO is independent with programming options for Edge or Level, COS (Change of State), Interrupt, Polarity. Programmable PLL plus on-board oscillator with secondary divider to supply COS reference frequency. Temperature Sensor with state-machine to manage serial interface. Industrial Temperature components. Rear IO (Pn4). Windows package supports all modes and comes with reference SW and test menu. Linux scheduled. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.10/2021 New Design cPCI3U32B1LPCIeX4. Converts the PCI bus used in cPCI to PCIe to allow use of PCIe modules in a cPCI system. 3.3V and 5V tolerant PCI bus with reverse bridge to create 1 lane PCIe interface. 4 lane connector provided to allow for multiple cable and interface options on the PCIe side. Local high stability 100 MHz generation with shunt to select Spread [SSC] or fixed clock [NSSC] operation. Industrial Temperature components. Support for 4 GPIO, EEPROM, External 12V for designs requiring additional current. 3U 4HP implementation. Transparent bridge does not require programming.

10/2021 Updated Design Parallel-TTL-GPIO Win10 Package. Available in XMC and PMC formats. 64 single ended IO with software programmable voltage reference [3.3V or 5V]. Each IO is independent with programming options for Edge or Level, COS, Interrupt, Polarity. Programmable PLL plus on-board oscillator with secondary divider to supply COS reference frequency. Temperature Sensor with state-machine to manage serial interface. Industrial Temperature components. Bezel IO with VHDCI connector and / or Rear IO from (PMC)Pn4, (XMC) Pn4 and/or Pn6

Win10 & Linux support packages. Driver and reference software set [UserAp]. See models tab for manual download - HW and SW.

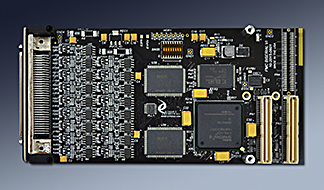

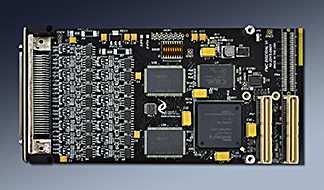

10/2021 Windows 10 package for UART model of PMC-BiSerial-VI.

8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. Alternate reference frequencies are available. Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.

Windows package supports all modes and comes with reference SW and test menu. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.

8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. Alternate reference frequencies are available. Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.

Windows package supports all modes and comes with reference SW and test menu. Reference HW and SW manuals available on the Dynamic Data Sheet. See the Models tab.09/2021 Updated Linux package for UART model of PMC-BiSerial-VI.

8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. Alternate reference frequencies are available. Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.

8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. Alternate reference frequencies are available. Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.Linux package supports all modes and comes with reference SW and test menu. Compatible with current kernels.

09/2021 Updated RTN10 model of PCI-ECL-II.

Custom Parallel interface. 8 bit parallel data path [NECL input and output] with reference clock and enable. Data valid on programmable edge of clock, enable active high. Programable use of enable. DMA support, 12 bits uncommitted TTL IO. Updated with higher performance memory operation, increased FIFO size, added status, and operational enhancements. Improved DMA performance and new Linux driver with this release.

Custom Parallel interface. 8 bit parallel data path [NECL input and output] with reference clock and enable. Data valid on programmable edge of clock, enable active high. Programable use of enable. DMA support, 12 bits uncommitted TTL IO. Updated with higher performance memory operation, increased FIFO size, added status, and operational enhancements. Improved DMA performance and new Linux driver with this release.

07/2021 New SpaceWire Monitor package by Dynamic Engineering. SpaceWire Monitor can be used to capture the communication between two SpaceWire nodes. Both sides are captured, filtered and stored to memory. Data is stored by packet and each packet is pre-pended with time, number and size. SpaceWire-Monitor can capture the data needed to do system / platform validation, debug tricky communications issues, capture HW data errors and more. Software is written in C and currently executes on Linux. The Monitor package is designed to utilize the latest Linux SpaceWire release [1.1.4]. SpaceWire-Monitor is a build option for PCI, PCIe, PMC, PC104p, and PCI-104 models of SpaceWire IO. All models offered have 576 KBytes of storage per port. DMA transfers data to the user specified file. NVMe or HDD with cache recommended for file storage. Data is stored as binary. Application includes binary conversion utility to provide human readable files. Click below for the SpaceWire-Monitor data page. Use the manuals tab to navigate to the user manual for more detail.

7/2021 Updated Design Parallel-TTL-GPIO Linux Package. Available in XMC and PMC formats. 64 single ended IO with software programmable voltage reference [3.3V or 5V]. Each IO is independent with programming options for Edge or Level, COS, Interrupt, Polarity. Programmable PLL plus on-board oscillator with secondary divider to supply COS reference frequency. Temperature Sensor with state-machine to manage serial interface. Industrial Temperature components. Bezel IO with VHDCI connector and / or Rear IO from (PMC)Pn4, (XMC) Pn4 and/or Pn6

Win10 & Linux support packages. Driver and reference software set [UserAp]. See models tab for manual download - HW and SW.

06/2021 New RMAP SpaceWire Linux software package by Dynamic Engineering. SpaceWire Remote Memory Access Protocol (RMAP) was developed to support reading and writing from/to memory in a remote SpaceWire.node. RMAP can be used to configure a SpaceWire network, control SpaceWire nodes, and transfer data between nodes. Software is written in C and currently executes on Linux. The RMAP package is designed to utilize the latest Linux SpaceWire release [1.1.4] and can be modified to work with other third party SW packages and other companies HW. Click below for the SpaceWire summary page. Use the manuals tab to navigate to the user manual for more detail.

06/2021 Updated SpaceWire Linux Driver and Reference SW by Dynamic Engineering. The new release features enhanced interrupt processing for multi-port DMA operation and modifications to support the RMAP Linux package. The driver has been validated on the P2020 platform (multi-core PPC) which is big endian and i7 for little endian operation. All 6 models of SpaceWire [K std, K-128, K-128RX, BK std, BK-128, BK-128RX] have been fully tested using the current FLASH release. Tested over the frequency range up to and including 200 MHz. HW/SW architecture supports full duplex line rate processing of back-to-back packet streams. PCI lane steering, driver auto detects endianess and controls HW accordingly. The updated FLASH supports improved DMA operation - changes made to improve port throughput and leveling of PCI access. Improved performance with small packets by adding to flow control. Please see the Hardware manuals for these details. Win10 and VxWorks also available.

6/2021 Solar Power Dynamic Engineering is pleased to announce that we have added approximately 54 KW of solar power generation to our location. With the addition of the solar panels Dynamic Engineering will be better than net 0 on an annual basis. Dynamic Engineering contracted with Just Leaks for the installation of the system. 133 panels with almost 3000 square feet of collection. Dual sided panels to take advantage of the reflected energy on a commercial reflective roof. Special rack mounts with hinges to allow for future maintenance on the roof without removing the panels. Three phase power generation to allow future connection with storage devices to support our Manufacturing and Engineering requirements.

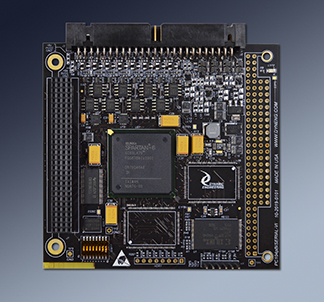

5/2021 Updated Design: PCIe8LXMCX1 Adapt an XMC into a PCIe system with PCIe8LXMCX1. 8 PCIe lanes routed to the XMC. Matched length controlled impedance traces suitable for Gen1-3. Options for FANs, rear IO connector types, and added external power. Bezel IO also supported. Internal Power Supplies for +5V, 3.3V, and -12V. +12V routed from PCIe interface. Updated with more current on the 5V and 3.3V supplies - with Rev 06 increased to 15A. Industrial Temperature components throughout. Power supplies allow user selection of delayed, immediate, and disabled for the +5V and +3.3V internal power supplies. If your XMC does not use one of the rails your inrush requirement can be reduced by disabling the unused supply. If your system has slow to program devices you will want the immediate turn on setting, and if your device is faster to load you can space out the inrush of the local supplies with the delayed setting. See Dynamic Data Sheet for more information and manuals.

3/2021 New Design cPCIBXMC3U32. Use your XMC in a cPCI environment. 3U 4HP adapter / carrier/ transition from cPCI to XMC standards. cPCIBXMC3U32 incorporates a 32 bit PCI interface [66 MHz capable, universal voltage] and converts to a single lane PCIe interface for the installed XMC device. The bridge is transparent - no SW development to use the adapter. XMC bezel aligns with cPCI bezel. XMC rear IO available with PMC style, XMC style or both connectors via cPCI J2. Industrial Temperature components. More information user manual available on Dynamic Data Sheet.

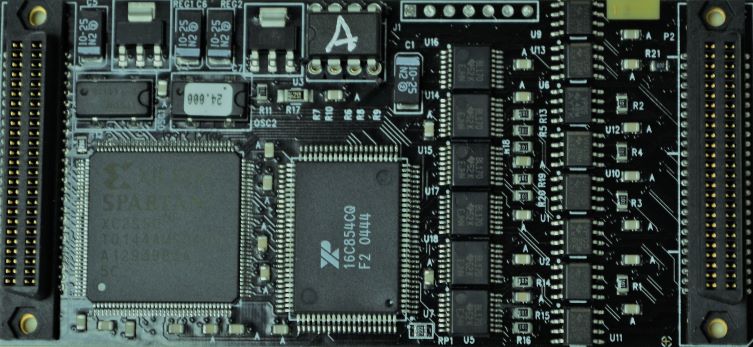

3/2021 Updated Designs PCI3IP, and PCI5IP - Added Features including VPWR plus upgraded to Spartan VI. PCI3IP features 3 IndustryPack Module positions in a half length PCI format design [Rev 11 and later]. PCI5IP incorporates 5 IP locations in a full length PCI format design [Rev 08 and later]. Both utilize industrial temperature devices. PCI3IP has been in production since 1999. PCI5IP since 2002. Through Dynamic Engineering´s continuous improvement plan the devices are still in production and serving our clients. If your system is PCI limited try the PCIe3IP and PCIe5IP models with similar features.

VPWR is the new name for the 5V rail supplied to the installed IndustryPack modules. 5V is the default to accomodate current designs. When the pin known as Reserved 1 [Pin 36] is grounded by one or more of the installed IP modules VPWR is switched to 3.3V as well as the reference to the terminations. Current FPGAs generally are not 5V tolerant plus require 3.3V for operation. The use of VPWR can save level translators and regulators on the IP Module.

Both of the updated designs are compatible with the unified DynEngIpCarrier driver, and DynEngIpCarrierAp. Driver and hardware support auto loading of IP Module drivers, access to each IP control register [carrier FPGA to control clock rate, interrupts, byte swapping, bus error, 32 bit conversion control etc.], Carrier registers for switch, revision, LEDs, interrupt status, etc. Full access to each of the IP address spaces [ID, IO, INT, MEM]. Reference Application provides examples of communicating with an IP in all address spaces, plus interrupts and handling bus errors. The reference SW for the carrier uses IP-Test as the target [modified IP-Parallel-HV]. IP Modules with Win10 driver packages have support specific to that module. Supported modules are auto-loaded. When an IP without a support package is detected IP-Generic is installed allowing use of third party IPs with the DynEngIpCarrier driver on a Dynamic Engineering IP Carrier.

3/2021 Updated Driver and Reference SW IP-Parallel-IO Win10 SoftWare package. The 7 standard models of IP-Parallel-IO [-TTL, -1, -2, -3, -4, -5, -485] are now supported with a unified Windows 10 reference software package. With this release all 7 models are covered. Revision 03 and 04 PCBs are compatible [Spartan II and Spartan 6 based designs]. The new unified driver package is compatible with the DynEngIpCarrier driver package. The new unified IpParIoUserAp has routines to demonstrate the use of the two counter timers, configuring and using the IO. Use of interrupts to manage the received IO and counter timers is included. Programming of the output waverform option is also included. The reference menu auto detects the type of IP installed and displays along with the details of that model. Carrier frequency of operation selection is demonstrated in the ATP Menu Item. The IOCTLs are grouped by _IO_ for common calls that apply to all 7 models, _N_ for calls specific to a particular model. The IOCTL is the same in all cases. The driver uses a common structure to communicate with the User program and auto alligns to the installed HW. A great reference to get you started. Included with your purchase of the IP-Parallel-IO family. HW and SW manuals available on the Dynamic Data Sheet - See link above or click on the photo.

2/2021 New Design Parallel-TTL-GPIO. Available in XMC and PMC formats. 64 single ended IO with software programmable voltage reference [3.3V or 5V]. Each IO is independent with programming options for Edge or Level, COS, Interrupt, Polarity. Programmable PLL plus on-board oscillator with secondary divider to supply COS reference frequency. Temperature Sensor with state-machine to manage serial interface. Industrial Temperature components. Bezel IO with VHDCI connector and / or Rear IO from (PMC)Pn4, (XMC) Pn4 and/or Pn6

Win10 support with Driver and reference software set [UserAp]. See models tab for manual download - HW and SW. Linux in development.

1/2021 Updated Design PMC-BiSerial-VI-HW1 is the ported and upgraded version of PMC-BiSerial-III-HW1. The updated version incorporates a Spartan VI FPGA, and industrial temperature components. These updates will allow for continued operation for years to come. SW compatible with the previous versions. Win10 and Linux SW packages. Linux available, Win10 in process. PMC-BiSerial-VI has 34 independent differential IO. Each of the IO have programmable termination, and direction controls. The IO is available for system connection through the front panel SCSI connector and / or Pn4. SCSI Cable and HDEterm68 can be used as a breakout for the IO.

The HW1 protocol implemented provides 32 Manchester encoded data ports per PMC-BiSerial-VI. Each port can operate with a selectable frequency, RX or Tx mode, unidirectional or bidirectional. CRC, Manchester, Ready_Busy, and other status provided. Internal Dual Port RAM blocks [512 x 32] used for each of the 32 channels. The 32 port plus 2 additional IO can be used for a parallel port. Bit level programmable for function, Direction, Termination. Option to use I2O or standard interrupts. The reference frequencies can be derived from the on-board oscillator or SW programmable PLL. The pin definitions are consistent with the PMC-BiSerial-III-HW1 design to allow migration to the PMC-BiSerial-VI-HW1 quickly and easily.

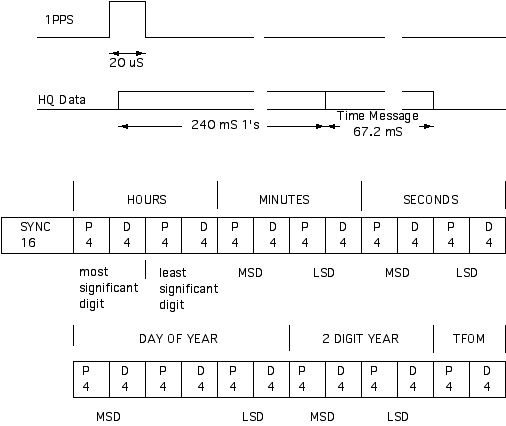

1/2021 Updated Driver and Reference SW For use with IP-HaveQuick- Win10 SoftWare package. IP-HaveQuick supports both Transmission and Reception of HaveQuick data. HaveQuick is a Time of Day interface. The 1PPS sync pulse is followed by manchester encoded data with the data and time. New with this release is a control bit that allows the user to select standard [Msb] and Lsb First operation. The ones, and synchronization pattern are not affected by the selection. The payload data and parity are reversed on a byte basis when selected. The Win10 package includes demonstrations of setting up the transmitter with the current data and time as well as receiving data via register reads or using the FIFO storage. Interrupt and polled operation supported and demonstrated. The new driver package is compatible with the DynEngIpCarrier driver package. A great reference to get you started. Included with your purchase of IP-PAR-HQT

1/2021 Facilities Improvement Dynamic Engineering has contracted to add approximately 54 KW of solar power to our electrical system. 3 phase system using 133 panels. Expected to be on-line in time for summer. The roof was recently redone to improve drainage and insulation value with a highly reflective surface. The Bifacial panels use the direct energy from the sun plus the reflected energy from the roof to generate electricity.

12/2020 Updated Driver and Reference SW For use with IP-Parallel-IO- Win10 SoftWare package. An integration effort is underway with the 7 standard models of IP-Parallel-IO [-TTL, -1, -2, -3, -4, -5, -485] to create a unified Win10 driver package. With this release the TTL and 485 models are covered. Revision 03 and 04 PCBs are compatible [Spartan II and Spartan 6 based designs]. The new unified driver package is compatible with the DynEngIpCarrier driver package. The new unified IpParIoUserAp has routines to demonstrate the use of the two counter timers, configuring and using the IO. Use of interrupts to manage the received IO and counter timers is included. The reference menu auto detects the type of IP installed. Frequency switching is demonstrated in the ATP option. The IOCTLs are grouped by _IO_ for common calls that apply to all 7 models, _485_ for calls specific to the -485 and _TTL_ for the TTL specific calls. A great reference to get you started. Included with your purchase of the IP-Parallel-IO family

10/2020 Updated Driver and Reference SW For use with PCIe3IP, PCIe5IP, PCI3IP, PCI5IP - Win10 SoftWare package. An integration effort is underway with the 4 models [PCI5IP, PCI3IP, PCIe5IP, PCIe3IP] now covered by the unified DynEngIpCarrier driver, and DynEngIpCarrierAp. cPCI and PC104p models will be added. Driver supports auto loading of IP Module drivers, access to each IP control register [in carrier FPGA to control clock rate, interrupts, byte swapping, bus error, 32 bit conversion control etc.], Carrier registers for switch, revision, LEDs, interrupt status, etc. Full access to each of the IP address spaces [ID, IO, INT, MEM]. Reference Application provides examples of communicating with an IP in all address spaces, plus interrupts and handling bus errors. The reference SW for the carrier uses IP-Test as the target [modified IP-Parallel-HV]. IP Modules with Win10 driver packages have support specific to that module. Supported modules are auto-loaded. When an IP without a support package is detected IP-Generic is installed allowing use of third party IPs with the DynEngIpCarrier driver on a Dynamic Engineering IP Carrier.

7/2020 New Product Announcement: PCIe-Harpoon

PCIe-Harpoon can be used for simulation, control, command and other embedded IO functions. The

Harpoonis being used for similation in its first applicaion. The client is using the Harpoon to simulate part of their system to allow testing of the rest of their system. The design has 4 channels to allow testing of multiple target hardware sets in parallel. Each channel has opto-isolated inputs set-up for 28V, High Side switches utilizing opto-coupled FETs with 60V 1.5A max per switch, Low Side switches also with opto-coupled FETs, 115V detection, and differential IO. The differential IO is configured to command and respond to the system under test. PCIe-Harpoon has a large FPGA to allow for customerized versions in new applications. Win10 driver and application software available. Cables and breakout [terminal strip] adapters also available.

Available now.

6/2020 Linux Driver IP-1553 now features a Linux support package. The hardware includes a Spartan VI FPGA and HOLT 1553 interface. These updates provide Mil-STD-1553 support in an IndustryPack format. Industrial temperature components throughout. SW compatible with the previous versions. Win10 and Linux SW packages. Control all aspects of the single (-1) or two port (-2) models. Each port is dual redundant with header options for direct and transformer coupled operation. IP-1553 Windows module driver is used with Dynamic Engineering IndustryPack carriers/drivers. For use with PCIe3IP, PCIe5IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP, PC104p4IP

6/2020 IP-BiSerial-VI-GPIO - New model of IP-BiSerial-VI released. The GPIO model features 24 differential IO configured as a parallel port. Each bit is programmable to be an input or an output. Polarity, Termination, Edge/Level interrupt triggering with separate Rising and Falling edge enables. Interrupt or polled operation. Direct and filtered data ports. User programmable PLL or local oscillator selection for COS reference. 485 and LVDS IO. Windows 10 and Linux support - see Dynamic Engineering IP carriers

[ PCIe3IP, PCIe5IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PCI-104, VPX2IP]. Industrial temperature standard.

IP-BiSerial-VI base features include: 24 independent differential IO each with programmable direction and termination. LVDS, RS485, and mixed IO types. Matched length, impedance controlled routing. Programmable PLL with 4 clock references. 8 and 32 MHz IP Module operation. Use this IndustryPack module to implement Manchester, Miller, Serial and Parallel IO, telemetry, communications, command and control etc. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information.

3/2020 Updated Design PMC-BiSerial-6T20 has been upgraded to incorporate a Spartan VI FPGA, and industrial temperature components. These updates will allow for continued operation for years to come. SW compatible with the previous versions. Win10 SW package. PMC-BiSerial-6T20 has 20 independent transformer coupled IO plus 2 direct connection differential IO. Each of the transformer coupled IO have resistive and capacitive coupling with SW control. The discretes have the resistive termination. The IO is available for system connection through the front panel SCSI connector. SCSI Cable and HDEterm68 can be used as a breakout for the IO. The pin definitions are consistent with the PMC-BiSerial-3T20 design to allow migration to the PMC-BiSerial-6T20 quickly and easily.

3/2020 Updated Design XMC-Parallel-TTL has been upgraded to incorporate a Spartan VI FPGA and VHDCI interface. These updates will allow for continued operation for years to come. Industrial temperature components throughout. SW compatible with the previous versions. Win10 SW package. XMC-Parallel-TTL has 64 independent digital IO. The high density makes efficient use of precious XMC slot resources. The IO is available for system connection both through the front panel and via the rear [Pn4, Pn6] connectors. A high density 68 pin VHDCI front panel connector provides the front panel IO. HDEterm68 can be used as a breakout for the front or rear panel IO. The pin definitions are consistent with the PMC-Parallel-IO design to allow migration to the XMC-Parallel-TTL quickly and easily.

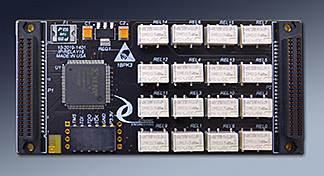

3/2020 New Design IP-Relay16 has been designed to support previous clients of the Systran IP-Relay16 design. 16 Form C relays. The relays are controlled by the host by setting or clearing bits in the Relay Control register. Each bit corresponds to one relay. When set the relay is energized. When cleared the relay is returned to the default state. Back EMF protection is provided on the control side of the relay. The voltage rating on each relay is up to 220 VDC, 250 VAC and 60W or 62.5 VA. The IP IO connector is limited to about 1 A per pin. The traces on the IP are rated for 1.5A. Industrial temperature components throughout. SW compatible with the previous versions. Win10 SW package. IP-Relay16 Windows module driver is used with Dynamic Engineering IndustryPack carriers/drivers. For use with PCIe3IP, PCIe5IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP, PC104p4IP

03/2020 Updated Driver and Reference SW Dynamic Engineering SpaceWire has an updated VxWorks Driver for Versions 6.9 and 7. The driver has been validated on the P2020 platform (multi-core PPC) which is big endian. All 6 models of SpaceWire [K std, K-128, K-128RX, BK std, BK-128, BK-128RX] have been fully tested using the current FLASH release. Tested over the frequency range up to and including 200 MHz. HW/SW architecture supports full duplex line rate processing of back-to-back packet streams. PCI lane steering, driver auto detects endianess and controls HW accordingly. The updated FLASH supports improved DMA operation - changes made to improve port throughput and leveling of PCI access. Improved performance with small packets by adding to flow control. Please see the Hardware manuals for these details. Line rate testing with the new Linux and Flash combination yielded 50 MBytes/sec continuous. Win10 and Linux also available.

2/2020 Updated Design IP-1553 has been upgraded to incorporate a Spartan VI FPGA and HOLT 1553 interface. These updates will allow for Mil-STD-1553 support in an IndustryPack format for years to come. Industrial temperature components throughout. SW compatible with the previous versions. Win10 SW package. Control all aspects of the single (-1) or two port (-2) models. Each port is dual redundant with header options for direct and transformer coupled operation. IP-1553 Windows module driver is used with Dynamic Engineering IndustryPack carriers/drivers. For use with PCIe3IP, PCIe5IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP, PC104p4IP

1/2020 Updated Driver package for KAON1 interface released - TTL and HOTLink interfaces with command / response type interaction. 2 Ports per ccPMC-HOTLink-KAON1. A new Win10 driver and reference software package has been developed. Linux also available.

The main purpose is to provide an interface to allow a PC or other computer to communicate directly with KAON1 interface. The KAON1 interface is bidirectional and utilizes both TTL and HOTLink serial interfaces. Each side is supported with large FIFOs. "Channelized DMA"™ on TX and RX. PLL support for custom frequencies. Please see the Dynamic Data Sheet [models tab] for links to HW and SW manuals with detailed information.

12/2019 Updated Hardware Release Dynamic Engineering has released an updated model - PCIe-SpaceWire. The PCIe-SpaceWire internal PCI bus now operates at 50 MHz for a 50% gain in bandwidth. The increase in BW means more ports can operate at higher frequencies with greater loading.

PCIe-SpaceWire implements SpaceWire [ECSS-E-ST-50-12C specification] in a convenient PCIe format. Four fully independent and highly programmable SpaceWire ports are provided by the PCIe-SpaceWire design. The SpaceWire protocol is advanced with link testing, error handling, command and data protocols built in. The SpaceWire electrical interface is point-to-point with token based flow control. With the SpaceWire protocol it is easy to build a heirarchical architecture system with routers or a home-run wired system. Your equipment can interact with any other node in the system. PCIe-SpaceWire provides a bridge from PCIe ⇔ SpaceWire. Port based DMA offloads the CPU and increases performance in your system. Time Code support provides a complete solution. Please refer to the HW manuals for detailed information. 200 MHz. Link rate, industrial temperature, DMA support, Windows, Linux, VxWorks support.

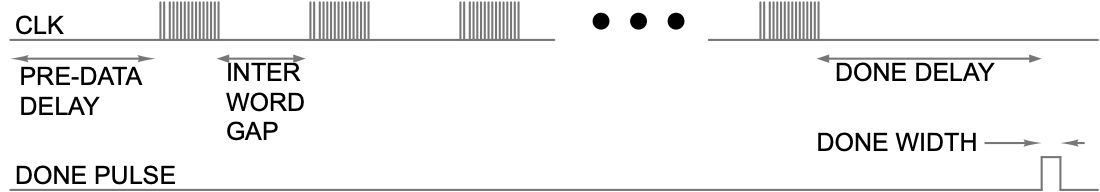

12/2019 IP-BiSerial-VI-BA27 - Update to BA27 model with more programmability. Added features include PDD = Pre Data Delay - a programmable delay from external trigger or SW enable to start transmitting, IWG = Inter Word Gap = a programmable delay between transmitted data, MultiCycle - operation with multiple words transmitted based on FIFO status. SingleCycle mode retained. 16,17,32,34 bit transfers. Msb/Lsb first operation. Programmable frequency. 485 and LVDS IO. Windows 10 and Linux support - see Dynamic Engineering IP carriers

PCIe3IP, PCIe5IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PCI-104, VPX2IP]. Industrial temperature standard.

IP-BiSerial-VI base features include: 24 independent differential IO each with programmable direction and termination. LVDS, RS485, and mixed IO types. Matched length, impedance controlled routing. Programmable PLL with 4 clock references. 8 and 32 MHz IP Module operation. Use this IndustryPack module to implement Manchester, Miller, Serial and Parallel IO, telemetry, communications, command and control etc. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information.

11/2019 Updated Driver package for ARC-210 interface released PCIe-BiSerial-DB37-LM9 supports communications with ARC-210 radios. A new Win10 driver and reference software package has been developed. Linux also available.

The main purpose is to provide an interface to allow a PC or other computer to communicate directly with an ARC-210 radio. The ARC-210 interface is bidirectional and is fully independent for Tx and Rx. Each side is supported with 4Kx32 Data FIFO plus 2Kx32 Packet FIFO. The transmitter "SendTiming" signal can be set to output the reference clock to allow for loop-back and alternate purpose uses. Interrupt or polled operation. "Channelized DMA"™ on TX and RX. 12 bit GPIO port [termination, direction independent on each bit]. RS-485 IO. TX in transmit SendTiming mode supported with PLL for user frequency. Please see the Dynamic Data Sheet [models tab] for links to HW and SW manuals with detailed information. This design can be ported to our other BiSerial formats - PMC, PCI-104 etc. Please contact Dynamic Engineering for these options.

11/2019 IP-BiSerial-VI-USR - user configurable / programmable FPGA based IP Module with 24 differential IO. Reference design [VHDL] available. On board FLASH to store the FPGA image for "instant on" operation. Windows and Linux support - see Dynamic Engineering IP carriers [PCI, PCIe, cPCI, PCI-104, VPX]. Industrial temperature standard. Spartan 6 LX25 device with block RAM and clocking elements to complete your design.

24 independent differential IO each with programmable direction and termination. LVDS, RS485, and mixed IO types. Matched length, impedance controlled routing. Programmable PLL with 4 clock references. 8 and 32 MHz IP Module operation. Use this IndustryPack module to implement Manchester, Miller, Serial and Parallel IO, telemetry, communications, command and control etc. Please see the Dynamic Data Sheet for links to HW and SW manuals and detailed information. Check the non-USR list - we may have your interface already imlemented.

9/2019 PMC2mPCI released PMC2mPCI is an adpater to convert between mPCI type III and PMC. It is a passive design with no additional SW required. Matched length, impedance controlled PCI bus with filtering. Mounts to any standard PMC location. Comes with mounting hardware. mini-PCI type III cards can add wireless and other interfaces to your PMC based project.