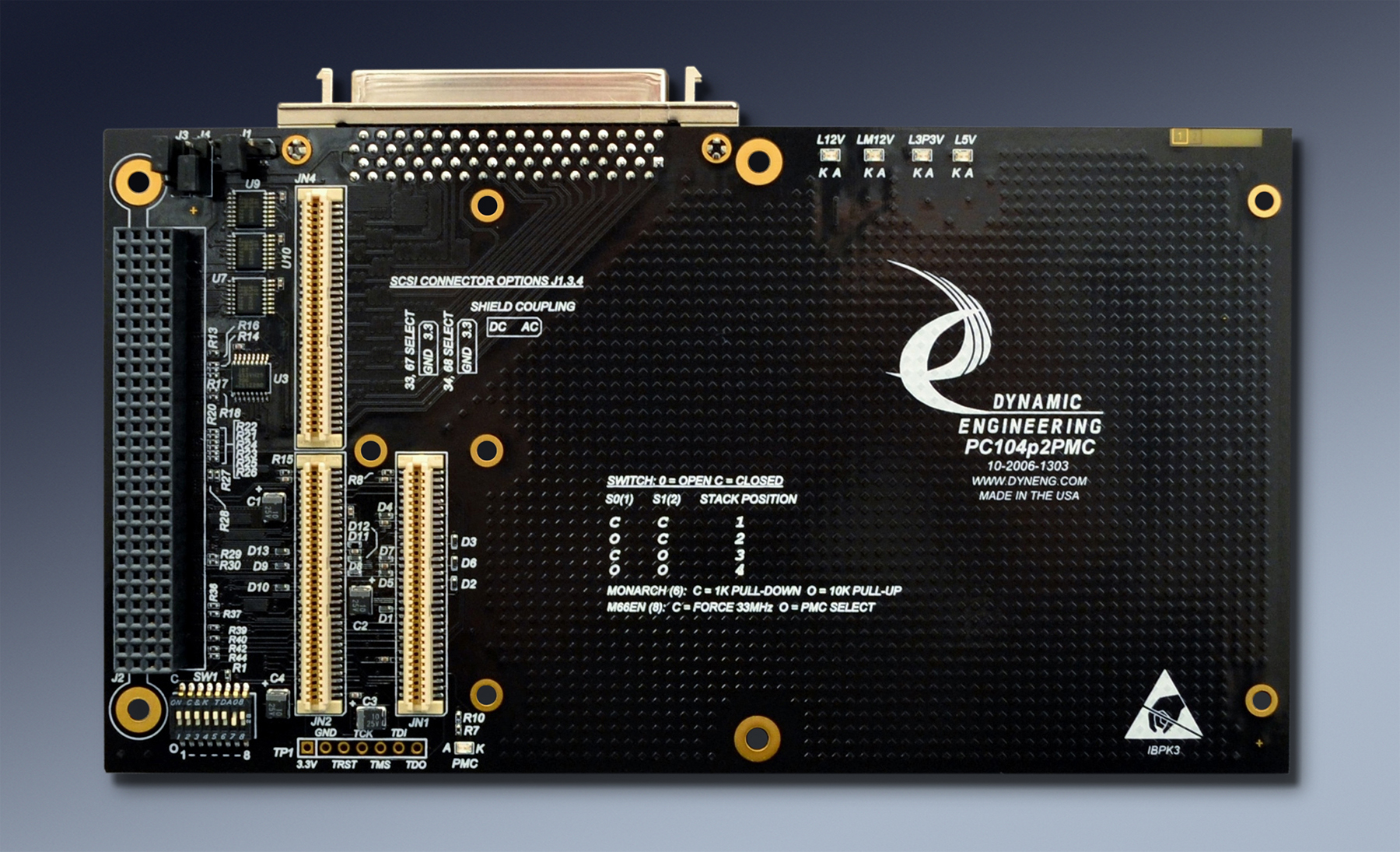

PC104p2PMC

PCI-104 adapter for PMC

Order This Item

PC104p2PMC Description

- Stack position selector

- Standard PMC module

- DMA operation supported. 33/66 MHz.

- PMC Bezel and/or rear IO

- Differential, impedance controlled Rear IO routing

- Power filtering

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature standard.

- ROHS and Standard processing available

PC104p2PMC ( PCI-104 to PMC ) adapter / carrier converter card provides the ability to install a PMC card into a standard PCI-104 slot. Suitable for PCI operation with 32 bit data and 33 or 66 MHz bus operation.

The PCI bus is buffered with 10 ohm series resistors and clamped with Schottky diodes. The PC104p2PMC design is passive with no added delays to access the PMC hardware. The traces are carefully routed with proper attention paid to the impedance, and reference planes to maximize compatibility with your PCI-104 system. PC104p2PMC is based on the highly successful passive PCI and cPCI carriers: PCI2PMC, and cPCI2PMC.

An optional connector "P1" is available for user IO from the Pn4 connector of your PMC. P1 is located in the standard connector area for PCI-104. P1 is routed to Pn4 using differential traces with matched length, and 100 ohm impedance control. Suitable for differential and non-differential IO. The connector shield can be AC/DC or open based on a user shunt. P1 has 4 "extra" pins which are selectable between open, 3.3V and ground [in pairs]. The voltage reference can be handy for low power external devices, in line terminations and loop-back fixtures.

The PCI bus interconnected to the PMC is a 66 MHz capable layout.

PCI VIO is interconnected to the PMC directly. The PCI-104 backplane will determine the bus voltage reference. The voltage select pins are not installed on the PC104p2PMC, and it is left to the user to properly select the PMC and PCI104 stack components for PCI voltage level considerations. Many PMCs are "universal" and can work with 3.3 or 5V PCI stacks.

PC104p2PMC uses planes for power distribution between the PCI-104 stack connector and the PMC connectors [Pn1 and Pn2]. .1 uF 50V caps are provided at each of the PMC power pins plus an additional 10 uF cap on the power rails.

The stack position is selected with the dipswitch. The interrupt, IDSEL, Clock, Bus Request and Bus Grant are selected based on the stack position.

LED´s are provided for the system voltages.

PMC JTAG connections are routed to a header for use with PMCs supporting JTAG programming. For example, most Dynamic Engineering PMC´s allow reprogramming the FPGA FLASH using the PMC JTAG FPGA connections.

If you have custom requirements please call or e-mail us with the details.

The PCI bus is buffered with 10 ohm series resistors and clamped with Schottky diodes. The PC104p2PMC design is passive with no added delays to access the PMC hardware. The traces are carefully routed with proper attention paid to the impedance, and reference planes to maximize compatibility with your PCI-104 system. PC104p2PMC is based on the highly successful passive PCI and cPCI carriers: PCI2PMC, and cPCI2PMC.

An optional connector "P1" is available for user IO from the Pn4 connector of your PMC. P1 is located in the standard connector area for PCI-104. P1 is routed to Pn4 using differential traces with matched length, and 100 ohm impedance control. Suitable for differential and non-differential IO. The connector shield can be AC/DC or open based on a user shunt. P1 has 4 "extra" pins which are selectable between open, 3.3V and ground [in pairs]. The voltage reference can be handy for low power external devices, in line terminations and loop-back fixtures.

The PCI bus interconnected to the PMC is a 66 MHz capable layout.

PCI VIO is interconnected to the PMC directly. The PCI-104 backplane will determine the bus voltage reference. The voltage select pins are not installed on the PC104p2PMC, and it is left to the user to properly select the PMC and PCI104 stack components for PCI voltage level considerations. Many PMCs are "universal" and can work with 3.3 or 5V PCI stacks.

PC104p2PMC uses planes for power distribution between the PCI-104 stack connector and the PMC connectors [Pn1 and Pn2]. .1 uF 50V caps are provided at each of the PMC power pins plus an additional 10 uF cap on the power rails.

The stack position is selected with the dipswitch. The interrupt, IDSEL, Clock, Bus Request and Bus Grant are selected based on the stack position.

LED´s are provided for the system voltages.

PMC JTAG connections are routed to a header for use with PMCs supporting JTAG programming. For example, most Dynamic Engineering PMC´s allow reprogramming the FPGA FLASH using the PMC JTAG FPGA connections.

If you have custom requirements please call or e-mail us with the details.

PC104p2PMC Features

Size

PC104p2PMC is a non-standard size PCI-104 board. The connector and mounting points are in the standard stack mounting locations. The board is elongated to add support and mounting positions for the installed PMC. Std PMC 74mm x 149mm will mount properly using the standard PMC mounting points. Step Files available.

IO

Front Bezel IO supported. Optional Pn4 "rear" IO is also available. Pn4 IO is routed with matched length, impedance controlled differential traces.

Clocks

PCI bus can operate at 66 or 33 MHz. The PMC must be 66 MHz capable for 66 MHz operation to work properly.

Access Width

Standard PCI byte lanes supported for byte, word and long access dependent on installed PMC. 32 bit operation supported.

Signal Conditioning

AD signals are series terminated with 10 ohm resistors. Schottky clamping Diodes on critical PCI signals. Zero delay buffer for PCI clock distribution.

Software Interface

PMC register definitions as defined by installed hardware. No software set-up required by PC104p2PMC.

Interrupts

INTA, B, C, D routed to PCI-104 / PC/104p connector from PMC.

Power

+5, +3.3, +12, -12V supplied to PMC. Power is filtered with decouplers on each PMC power pin plus bulk.

LEDs

PCI3.3, +3V, +5V, +12V, -12V and Busmode 1

JTAG

PMC JTAG connections are routed to a header. JTAG pin definitions are in the silkscreen. Handy for use with PMC´s supporting JTAG FPGA programming.

VIO

PCI IO Voltage is set by the PCI backplane. VIO is routed from the PCI-104 connector to the PMC

Export Classification

EAR99, HTS:8537.10.9050

PC104p2PMC Benefits

Speed

With the PC104p2PMC direct connect to the PCI bus the latency to the PMC is optimized. Your data will move quickly and reliably through the PCI bus to and from your hardware.

Price

PC104p2PMC has an attractive price point. Make use of existing PMC designs in PCI-104 and PC/104p applications without paying for the expense of a new design and layout. Quantity discounts are available.

Quantity discounts available

Quantity discounts available

Ease of Use

PC104p2PMC is designed to be easy to use. Direct access to all features, aligned registers for larger access types, programmable features to allow personalization for your system. Please download the manuals and see for yourself. Reference software is provided in source form to get you started.

Availability

The standard model of PC104p2PMC is on our stocked item list. Generally available for immediate shipment, with Dynamic Engineering´s on-site manufacturing temporary out of stock situations are resolved quickly.

PMC Specification Compatibility

PC104p2PMC is compliant per the VITA PMC/CMC specifications. All Dynamic Engineering PMC Modules are compatible with PC104p2PMC. Any PMC specification compliant design should work with this interface.

PCI Compatibility

PC104p2PMC is PCI compliant. PC104p2PMC is routed as an extension of the stack. The trace lengths, impedance and other routing characteristics are controlled to provide a reliable PCI connection at the PMC connector. Since the trace length with the PMC installed will be longer than a standard PC104p card, the PC104p2PMC design includes 10 ohm series resistors, and clamping diodes help to control the AD and control signals. PC104p2PMC adapters can be expected to work in any PCI bus stub.

Part Number: PC104p2PMC

Ordering Options

- PC104p2PMC Standard board

- -IO for standard PC104p2PMC with Pn4 to SCSI (P1) rear IO

- -ROHS Use ROHS processing. Standard processing is ""leaded"

- -CC Option to add Conformal Coating

PC104p2PMC Drivers

Software Support PC104p2PMC is a passive design with no carrier/adapter driver required. Use the installed PMC driver directly. Please see the Driver manuals for the specifics of each type.