PCIe8LXMCX2CB

PCIe adapter for XMC with 2 XMC positions and internal Connector Bus

Order This Item

PCIe8LXMCX2CB Description

- Industrial Temperature

- PCIe 1-8 Lane Interface

- 2 XMC Positions with PCIe Interface Supporting Gen1(2.5 Gbps) and Gen 2 (5 Gbps)

- Plug and Play operation

- Local Power Supply for 3.3, 5 and -12V Operating from System +12V

- Full Length PCIe Card

- "Zero Slot Fan"™ Compatible

- Bezel I/O and Jn4/Jn6 I/O for both XMC´s

- Resistor programmable "Connector Bus" between J04/J06 and J14/J16

- 1 Year Warranty Standard. Extended Warranty Available.

- ROHS and Standard Processing Available

Embedded applications frequently require real time processing coupled with special purpose IO. With the PCIe8LXMCX2CB´s two positions a PrXMC can be matched with another XMC to make a high bandwidth processing node. The PrXMC can communicate with the host for set-up, and then use the switch to interconnect with the special purpose IO card. With a local processing node of this nature you can use many in parallel with only one computer to provide the system management. For example - 10 in an expansion chassis without overloading the buses or management system.

The CB version of PCIe8LXMCX2 has the option to connect each XMC to the standard IO, the connector bus - either, neither or both. The connector bus creates a matched length, impedance controlled, differentially routed interconnection between the two XMC positions. The bus can be used for direct connection between the cards without going through the PCIe links. High speed control, specialized communications, signal processing etc. can be faciliated by the specialized connection. Please refer to the HW manual for tables showing the connection options. Select the desired connections and submit to Dynamic Engineering. An updated machine programming file can be generated to install the desired connections to the IO and between each position. There are 64 positions for each connector. To eliminate stubs and provide the highest possible performance 4 resistors are used per IO pin. The resistors allow the Jn4/Jn6 connections to be isolated as well as the IO and CB connections. 512 possible resistors to install. Usually a subset will be installed since signals will normally be connected to Jn4 or Jn6 and not both and either IO or CB and not both.

A powerful PCIe 24 lane switch is at the center of the PCIe8LXMCX2CB design. The switch has many capabilities including operating from 1-8 lanes, operating at Gen 1 or Gen 2 or mixed IO rates, supports lane reversal and polarity inversion (in case your XMC is not quite right), Support for max payload size transfers up to 2048 bytes ea., fully compliant with the PCIe base specification 2.0. The switch has 8 PCIe lanes connected to the PCIe "gold fingers" and 8 to each of the XMC´s. The PCIe reference clock is buffered with a Gen1/Gen2 compatible clock buffer. The clock buffer is specifically designed to handle spread spectrum and rate locked clocking operation. The buffered clocks are routed to the switch and the two XMC positions. A local power supply and heavy filtering insure stable power and reliable operation for the switch. The PCIe lanes to/from the switch are routed per PCIe specifications with matched lengths and impedance control.

PCIe8LXMCX2CB (PCIexpress Bridge PMC 2 slots) adapter / carrier converter card provides the ability to install two XMC cards into a standard PCIe slot. Slots with 8 or more lanes are compatible - 8, or 16 for example. PCIe8LXMCX2CB has two XMC card positions. XMC operation with 2.5 Gbps or 5 Gbps. PCIe8LXMCX2CB can act as a transparent switch or be programmed to allow private operations on the back side [PCIe] bus.

XMC user IO connector Pn4 or Jn6 from both positions is brought out to one of two connectors for access (DIN IDC or SCSI II). The signals corresponding to the PrXMC [position 0] standard Ethernet and Serial lines can optionally be connected to the Ethernet and Serial port connectors at the top edge of the board. The signals are isolated with resistor packs to keep the routing short. The XMC front panel connector for slot 1 is mounted though the PCIe mounting bracket.

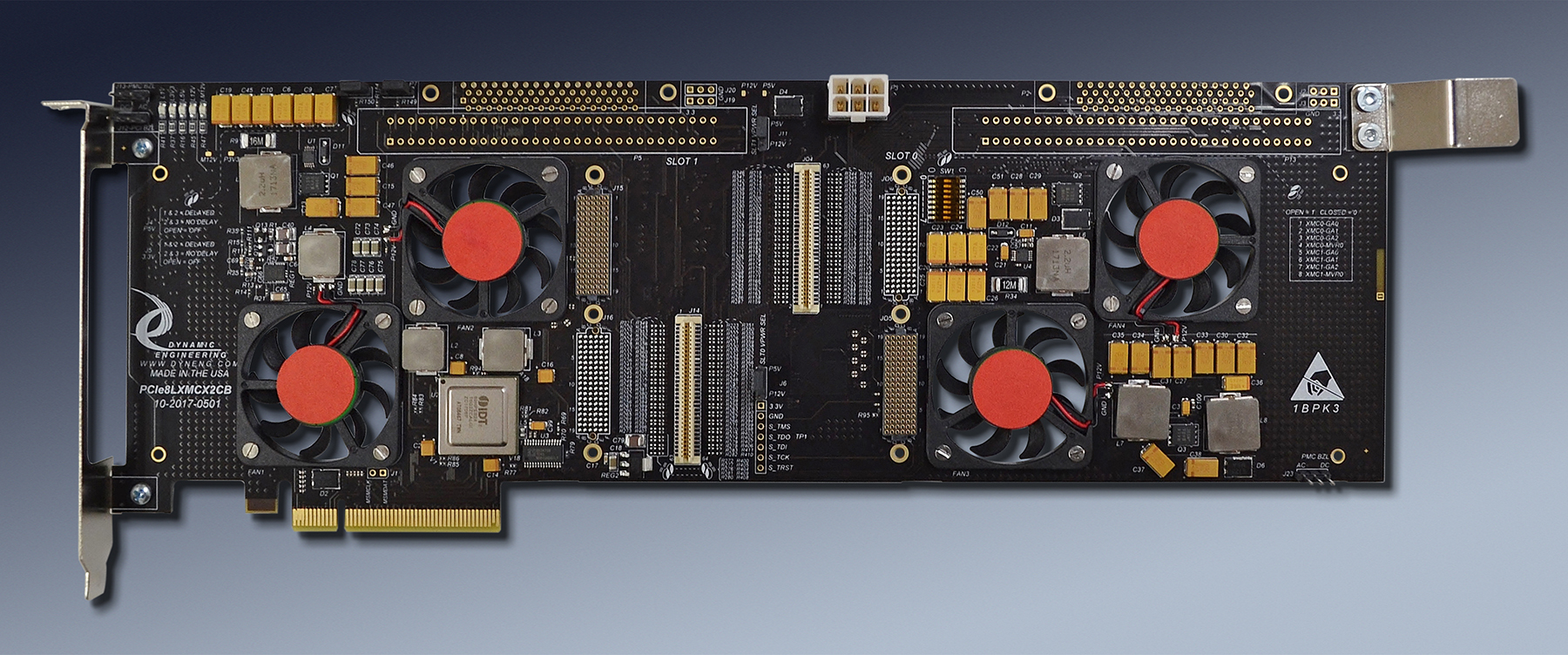

For superior performance PCIe8LXMCX2CB has two cooling cutouts per position for increased airflow to the XMC´s. If your application requires a fan you can order PCIe8LXMCX2CB-FAN( ) to have fans mounted to your PCIe8LXMCX2CB. FAN positions are numbered 1-4, position 1 is closest to the PCIe Bezel [left edge in the picture above.] One fan can be mounted per position. Fans can be mounted to blow onto the XMC or to pull air from the XMC (R option.)

The -12V, 5V, and 3.3V for the XMC are regulated on board. The power supply designs utilize switching regulators controlling a MOSFET to convert 12V. An LC filter ensures clean power at the XMC. The Switch uses a small amount of 3.3 and power derived from 3.3V plus 1.0V derived from +12.. The PCIe gold fingers are rated for 1.1A each, and a total of 5.5A on the +12V rail. 55W are available to the XMC´s after power conversion. Please note this is the combined power requirement across the +12, -12, +5, and 3.3V power used by the XMC´s. In most cases 55W is sufficient. PCIe8LXMCX2CB has a cable connector to allow additional 12V power to be added to the card. The two supplies are DIODE coupled. In some cases the 12V supply on the backplane will not be adequately routed by the PC causing voltage sag on the 12V. If this occurs use the cable connector to compensate.

The power supplies include the bulk capacitance to properly bypass the FET´s and post conversion voltage rails. In addition the XMC connectors are bypassed with a .1 uF capacitor at each power pin. The power supplies are checked with voltage monitor circuits. The LED´s are not illuminated unless the voltage is within the defined range. A new feature added with the current revision is the addition of two headers to allow user selection of 5V and 3.3V power on characteristics. The user can select [with shunts] Instant On, Delayed On, and disabled. If your design does not use one of the rails you can turn it off. If your system enumerates early in the power up cycle you can select instant on. If your system can use the delayed load on the power supply to advantage select delayed.

The XMC specification calls out "VPWR " which can be either 12V or 5V. PCIe8LXMCX2CB has FET switching and a header to allow user selection of either 12V or 5V or neither voltage to be supplied to these 8 pins [per XMC]. The selection is separate per XMC position. Build options are provided to allow "pre selected" voltages on these pins without the headers. The 12V asnd 5V supplied are part of the same power budget mentioned above. It is suggested the user select the rail definition most efficient for use, alternatively based on noise, the 5V will likely be quieter since it is converted on board and isolated from the 3.3V rail.

The individual pins on the Jn4 (PN4) and Jn6 [Pn6] connectors for each slot are accessible by either a 68 pin SCSI connector or a 64 position DIN connector. The IO are routed with matched length, impedance controlled differential traces suitable for single ended and differential operation. We recommend using our SCSI cable and the HDEterm68 breakout block with the SCSI connector. The industry standard VME IDC [DIN] connector is easy to connect to your system using DINterm64 which is a 64 position terminal strip and the DIN Ribbon Cable 64, a 64 position ribbon cable. The inter-connection from Jn4 and Jn6 to either the SCSI or DIN connectors are documented in the manual. Please see below.

The XMC JTAG connections for slot 0 are routed to a header. Please let us know if you want this header installed. [-JTAG]

The PCIe bus does not have a concept of global addressing. A DIPSWITCH is provided to allow the user to select the Global Address on both XMC positions individually.

The CB version of PCIe8LXMCX2 has the option to connect each XMC to the standard IO, the connector bus - either, neither or both. The connector bus creates a matched length, impedance controlled, differentially routed interconnection between the two XMC positions. The bus can be used for direct connection between the cards without going through the PCIe links. High speed control, specialized communications, signal processing etc. can be faciliated by the specialized connection. Please refer to the HW manual for tables showing the connection options. Select the desired connections and submit to Dynamic Engineering. An updated machine programming file can be generated to install the desired connections to the IO and between each position. There are 64 positions for each connector. To eliminate stubs and provide the highest possible performance 4 resistors are used per IO pin. The resistors allow the Jn4/Jn6 connections to be isolated as well as the IO and CB connections. 512 possible resistors to install. Usually a subset will be installed since signals will normally be connected to Jn4 or Jn6 and not both and either IO or CB and not both.

A powerful PCIe 24 lane switch is at the center of the PCIe8LXMCX2CB design. The switch has many capabilities including operating from 1-8 lanes, operating at Gen 1 or Gen 2 or mixed IO rates, supports lane reversal and polarity inversion (in case your XMC is not quite right), Support for max payload size transfers up to 2048 bytes ea., fully compliant with the PCIe base specification 2.0. The switch has 8 PCIe lanes connected to the PCIe "gold fingers" and 8 to each of the XMC´s. The PCIe reference clock is buffered with a Gen1/Gen2 compatible clock buffer. The clock buffer is specifically designed to handle spread spectrum and rate locked clocking operation. The buffered clocks are routed to the switch and the two XMC positions. A local power supply and heavy filtering insure stable power and reliable operation for the switch. The PCIe lanes to/from the switch are routed per PCIe specifications with matched lengths and impedance control.

PCIe8LXMCX2CB (PCIexpress Bridge PMC 2 slots) adapter / carrier converter card provides the ability to install two XMC cards into a standard PCIe slot. Slots with 8 or more lanes are compatible - 8, or 16 for example. PCIe8LXMCX2CB has two XMC card positions. XMC operation with 2.5 Gbps or 5 Gbps. PCIe8LXMCX2CB can act as a transparent switch or be programmed to allow private operations on the back side [PCIe] bus.

XMC user IO connector Pn4 or Jn6 from both positions is brought out to one of two connectors for access (DIN IDC or SCSI II). The signals corresponding to the PrXMC [position 0] standard Ethernet and Serial lines can optionally be connected to the Ethernet and Serial port connectors at the top edge of the board. The signals are isolated with resistor packs to keep the routing short. The XMC front panel connector for slot 1 is mounted though the PCIe mounting bracket.

For superior performance PCIe8LXMCX2CB has two cooling cutouts per position for increased airflow to the XMC´s. If your application requires a fan you can order PCIe8LXMCX2CB-FAN( ) to have fans mounted to your PCIe8LXMCX2CB. FAN positions are numbered 1-4, position 1 is closest to the PCIe Bezel [left edge in the picture above.] One fan can be mounted per position. Fans can be mounted to blow onto the XMC or to pull air from the XMC (R option.)

The -12V, 5V, and 3.3V for the XMC are regulated on board. The power supply designs utilize switching regulators controlling a MOSFET to convert 12V. An LC filter ensures clean power at the XMC. The Switch uses a small amount of 3.3 and power derived from 3.3V plus 1.0V derived from +12.. The PCIe gold fingers are rated for 1.1A each, and a total of 5.5A on the +12V rail. 55W are available to the XMC´s after power conversion. Please note this is the combined power requirement across the +12, -12, +5, and 3.3V power used by the XMC´s. In most cases 55W is sufficient. PCIe8LXMCX2CB has a cable connector to allow additional 12V power to be added to the card. The two supplies are DIODE coupled. In some cases the 12V supply on the backplane will not be adequately routed by the PC causing voltage sag on the 12V. If this occurs use the cable connector to compensate.

The power supplies include the bulk capacitance to properly bypass the FET´s and post conversion voltage rails. In addition the XMC connectors are bypassed with a .1 uF capacitor at each power pin. The power supplies are checked with voltage monitor circuits. The LED´s are not illuminated unless the voltage is within the defined range. A new feature added with the current revision is the addition of two headers to allow user selection of 5V and 3.3V power on characteristics. The user can select [with shunts] Instant On, Delayed On, and disabled. If your design does not use one of the rails you can turn it off. If your system enumerates early in the power up cycle you can select instant on. If your system can use the delayed load on the power supply to advantage select delayed.

The XMC specification calls out "VPWR " which can be either 12V or 5V. PCIe8LXMCX2CB has FET switching and a header to allow user selection of either 12V or 5V or neither voltage to be supplied to these 8 pins [per XMC]. The selection is separate per XMC position. Build options are provided to allow "pre selected" voltages on these pins without the headers. The 12V asnd 5V supplied are part of the same power budget mentioned above. It is suggested the user select the rail definition most efficient for use, alternatively based on noise, the 5V will likely be quieter since it is converted on board and isolated from the 3.3V rail.

The individual pins on the Jn4 (PN4) and Jn6 [Pn6] connectors for each slot are accessible by either a 68 pin SCSI connector or a 64 position DIN connector. The IO are routed with matched length, impedance controlled differential traces suitable for single ended and differential operation. We recommend using our SCSI cable and the HDEterm68 breakout block with the SCSI connector. The industry standard VME IDC [DIN] connector is easy to connect to your system using DINterm64 which is a 64 position terminal strip and the DIN Ribbon Cable 64, a 64 position ribbon cable. The inter-connection from Jn4 and Jn6 to either the SCSI or DIN connectors are documented in the manual. Please see below.

The XMC JTAG connections for slot 0 are routed to a header. Please let us know if you want this header installed. [-JTAG]

The PCIe bus does not have a concept of global addressing. A DIPSWITCH is provided to allow the user to select the Global Address on both XMC positions individually.

PCIe8LXMCX2CB Features

Size

Full size PCIexpress card with 8 lanes interconnected to the XMC positions via 8x8x8 [24 lane] switch. 1-8 lane operation. 8+ lane connector compatible.

XMC compatible slots

2 XMC positions provided.

Clocks

Gen1 and Gen2 compatible.

Global Addressing

Supported with a user DIPSWITCH

Software Interface

The switch does not require any user set-up. XMC register definitions as defined by installed hardware. XMC register definitions as defined by installed hardware.

Power

Local power supplies provide +5(10A), +12, -12V(4A), +3V(10A) available to XMC´s with adequate +12V input current. Supplies use industrial temperature components, and spreading power planes to manage the thermal load. It is recommended to use the FAN option for high power requirement XMC´s. User selectable power supply enable{on/off, delayed, not delayed] for 3.3V and 5V supplies

VPWR

VPWR for each position can be programmed independently.� Options for user selection, or pre-selected to 5V or 12V.

Thermal

PCIe8LXMCX2CB has cut-outs to support increased airflow over the XMC´s component side. Optional fan(s) with two mounting positions per XMC position are available and recommended for many applications.

Interrupts

PCIe MSI interrupt scheme is supported

IO Interface

XMC Bezel IO supported at PCIe bracket. Jn4 / Jn6 "user IO" supported with either SCSI or DIN connectors at both positions. See Panduit for mate [120-964-455] or standard SCSI II connector.

CB Interface

In addition to the IO connections Jn4 / Jn6 can be interconnected between the XMC´s to provide a customized inter-XMC bus. The connections are designed to provide high speed bus(es) with matched length, controlled impedance almost zero stub length routing between. Use the table in the HW manual to indicate the connections you want. A small, onetime charge applies to program our SMT assembly machine, a new extension to document the configuration will be used to order that resistor set.

Specification

XMC, PCIe specification compliant

LED´s

+3V, +5V, 1.0V, +12V, -12V. LED´s on voltages illuminated via monitoring circuits which check that the voltages are within tolerance.

JTAG

XMC JTAG connections are tied to a labeled header. Add -JTAG to part number for this option to be installed.

Statement of Volatility

Reliability

TBD hours. Bellcore. GB 25c

STEP

STEP files are available to support your system integration. Please contact sales@dyneng.com for this option.

PCIe8LXMCX2CB Benefits

Speed

PCIe8LXMCX2CB offers Gen1 andf Gen2 speeds plus a second XMC position for designs with more than one XMC. Double the IO in one carrier. When local processing is needed, the rear position can be used with a PrXMC and the IO or signal processing in the front position. The Host computer can set-up operation, and then the PrXMC can use the inter-switch connections for high speed data transfer with second XMC.

Price

Make use of existing XMC designs in PCIe applications without paying for the expense of a new design and layout. Save PCIe slots with two XMC´s in one location. Use multiple PCIe8LXMCX2CB´s in parallel without overloading your host processor to reduce system cost. Quantity discounts are available.

Ease of Use

PCIe8LXMCX2CB is easy to use. The XMC´s installed are directly controlled via the PCIe lanes.

Availability

The standard versions are built in quantity allowing for rapid addition of "Zero Slot Fans"™ and other options. Send in your order for rapid delivery.

Size

PCIe8LXMCX2CB is a full size PCIe board which conforms to the PCIe mechanical and electrical specifications. Eliminate mechanical interference issues. PCIe8LXMCX2CB can be used in all full length PCIe compliant slots. Please check that your computer has a full length slot with the proper PCIe offset card guide support.

XMC Compatibility

PCIe8LXMCX2CB is XMC compliant per the XMC specification. All Dynamic Engineering XMC Modules are compatible with the PCIe8LXMCX2CB. All other XMC Modules which are compliant with the XMC specification are compatible with PCIe8LXMCX2CB

PCIe Compatibility

PCIe8LXMCX2CB is PCIe compliant. PCIe8LXMCX2CB can be expected to work in any PCIe compliant backplane with 8+ lane connectors and full length card positions. PCIe8LXMCX2CB has been tested in multiple backplanes.

Part Number: PCIe8LXMCX2CB

Ordering Options

- PCIe8LXMCX2CB Standard board - for a base version (PCIe8LXMCX2CB-DIN) and standard processing

- -FAN( ) Need additional cooling? Order PCIe8LXMCX2CB-FAN( ) for a pre-installed 12V 5.2CFM fan(s) to maximize cooling and functionality of your card. The fan has been tested with high wattage PrPMC devices. Fan position 1 is closest to the PCIe bezel. Valid Fan options include: (1,1Rz), (2,2Rz), (3,3Rz), (4,4Rz), low profile fans with fan direction toward XMC or pulling air from the XMC [R]. An additional option is to use standard height fans with more LFM. 8 CFM fans are available as rear mount only (add -FAN(1,2,3,4)R to PN for this option)

- -ROHS Use ROHS processing. Standard processing is ""leaded"

- -CC Option to add Conformal Coating

- -NC Order to receive a PCIe8LXMCX2CB with no SCSI or DIN connectors installed.

- -XIO Order to receive a PCIe8LXMCX2CB with Jn6 installed as well as Jn4

- -XIOExc Order to receive a PCIe8LXMCX2CB with Jn6 installed exclusively [no Jn4]

- -VPWR5V Order to receive a PCIe8LXMCX2CB with VPWR forced to 5V instead of user selectable

- -VPWR12V Order to receive a PCIe8LXMCX2CB with VPWR forced to 12V instead of user selectable

- -5VXXX Order to receive a PCIe8LXMCX2CB with 5V supply forced to (replace XXX) No Delay [ND], Delay[DEL], Off[OFF] instead of user selectable

- -3VXXX Order to receive a PCIe8LXMCX2CB with 3.3V supply forced to (replace XXX) No Delay [ND], Delay[DEL], Off[OFF] instead of user selectable

- -AP Order to receive a PCIe8LXMCX2CB with a PC standard 2x3 connector installed for supplemental power.

PCIe8LXMCX2CB Drivers

Software Support for PCIe8LXMCX2CB is not needed. PCIe8LXMCX2CB is a switch based card, the drivers and application SW associated with the XMC will not need changing based on using this carrier.

Please see the XMC Driver manual for the specifics of operating the installed device.

Please see the XMC Driver manual for the specifics of operating the installed device.

PCIe8LXMCX2CB Manuals

PCIe8LXMCX2CB Hardware Design Manual Main product manual with example use, pinouts, specifications and more.