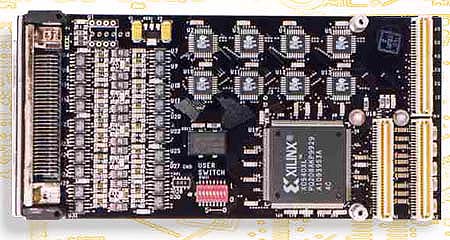

PMC-BiSerial-S311

PMC Compatible 4 channel Transmit Serial Data Interface

PMC-BiSerial-S311 Block Diagram

PMC-BiSerial-S311 Timing

Please note PMC-BiSerial has been upgraded and PMC-BiSerial-VI is currently recommended for new designs

The PMC-BiSerial-S311 implements the Northrop Grumman S-311 interface protocol. This protocol uses a burst clock to shift 18 bits of data. The data changes on the rising edge of the clock and is valid on the falling edge. The first bit is the sync bit, which is always high and the next 8 bits are the upper byte of the data shifted out MSB first. The next bit is the mode bit, which is zero for a data word and one for a command word. The final 8 bits are the lower byte of data shifted out MSB first.

Two additional signals are used in this protocol, request and ready. The request signal is asserted high by the transmitter at least two clock periods before the first clock. The request signal also remains asserted at least two clock periods after the falling edge of the last clock. After request goes low, at least four clock periods must elapse before it is reasserted. The ready signal is asserted high by the receiver when it is ready to receive data i.e. it has been started and the Rx FIFO is not full. The ready signal can remain high between words as long as the receiver is able to receive data. No data should be transmitted unless ready is high, or does not exist.

The serial channels are each supported by a 4K by 32 bit FIFO (see block diagram). The FIFO supports long word reads and writes. A path exists for loop-back testing of each FIFO. The PMC data path is 32 bits wide, while the data path from the FIFO to the Xilinx is 8 bits wide. The hardware automatically performs the 4 data accesses and byte lane manipulation to make the internal port appear as a 32-bit port to the PMC bus. The design is optimized for the system configuration with minimal delay on the PCI write to TX FIFO path and PCI read from the RX FIFO path. The added delay for reading and writing to the internal FIFO ports only affects the loop-back test path.

As the serial receive channel receives data, MSB first, it is stored in 18-bit words with the sync bit in the MSB (bit 17), the mode bit repositioned to bit 16 and the 16 data bits stored in bit 15 down to 0. The host can poll the empty flag status or use the programmable FIFO Almost Full flag to determine when data is available. The message can be read directly from the input FIFO.

The Output channel has a separate 4K x 32 FIFO. The FIFO is written as long words with the sync bit in bit position 17, the mode bit in bit position 16 and the 16 data bits in bit positions 15 to 0. Data is sent MSB first with the sync bit first followed by eight data bits, the mode bit, and the final eight data bits. Data is sent whenever the transmitter is enabled and data is stored within the FIFO and the ready signal is asserted from the receiver. Transmission completes and the transmitter is disabled when the FIFO becomes empty.

Interrupts are supported by the PMC-BISERIAL. For the S311 version, interrupts can be generated by the following conditions: transmission complete; transmitter almost empty; receiver almost full; receiver overflow; and a receiver interrupt, which can be configured to respond to any word received, or for a word received with a specific mode bit value, either zero or one.

The interrupts are individually maskable and a master interrupt enable is also provided as well as a force interrupt bit for testing purposes. The interrupt occurs on INTA. The FIFO levels and other status are also available for operating in a polled mode, if desired.

Reliability

864,882 hours. Bellcore. GB 25c

82,891 hours. Bellcore. GB 70c Note: with commercial parts, -ET is available

If your situation demands a custom application then we will update the Xilinx FPGA. Send us your timing and we will send you the interface....

email us your wish list or call today!

Order Information

PMC-BiSerial-S311 PMC BiSerial with S311 interface

PMC-BIS-Eng-Kit1..........Engineering Kit for PMC-BiSerial includes Board level Schematics [PDF], Reference Software [Win7 driver and reference application], HDEterm68-MP, HDEcabl68

Related: 68 position terminal strip to SCSI III connector adapter and BiSerial compatible SCSI III cable

You must have Adobe Acrobat to read our PDF files.

Hardware Manual: S311 HW Manual

Driver Manuals:

PMC-BiSerial-S311 WinNT Installation and Use Manual

PMC-BiSerial-S311 Win7 Installation and Use Manual

Custom, IP, cPCI, PC104p, PCIe104, PMC, XMC, PCI, PCIe, VME, VPX Hardware, Software designed to your requirements

Home |

News |

Search the Dynamic Engineering Site

[an error occurred while processing this directive]