#### DYNAMIC ENGINEERING

150 DuBois St., Suite B&C Santa Cruz, CA 95060 (831) 457-8891

<a href="mailto:https://www.dyneng.com">https://www.dyneng.com</a>

<a href="mailto:sales@dyneng.com">sales@dyneng.com</a>

<a href="mailto:Est. 1988">Est. 1988</a>

**User Manual**

# SpaceWire "BK" Model Hardware Manual

Four-Channel SpaceWire Interface PCIe, PCI, PC104p, PMC Versions

Manual Revision 4p0

PCI-SpaceWire

Corresponding Hardware: 10-2006-01(04)

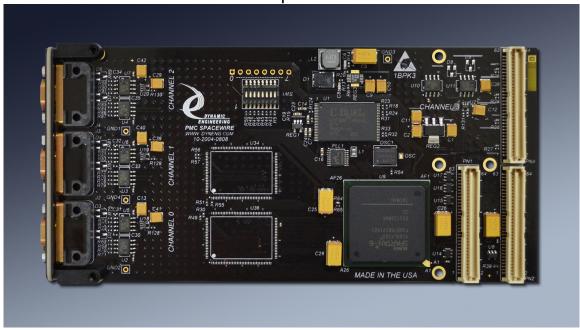

PMC-SpaceWire

Corresponding Hardware: 10-2004-08(08,09)

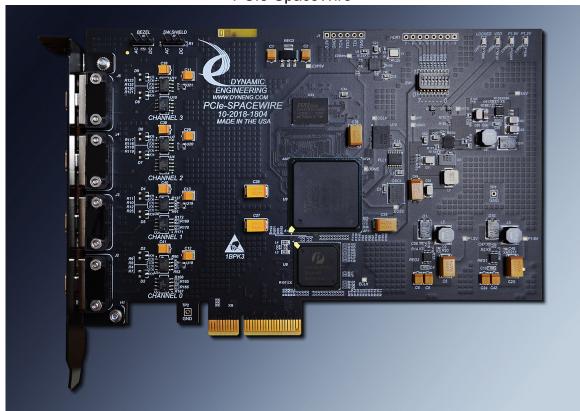

PCIe-SpaceWire

Corresponding Hardware: 10-2018-1804

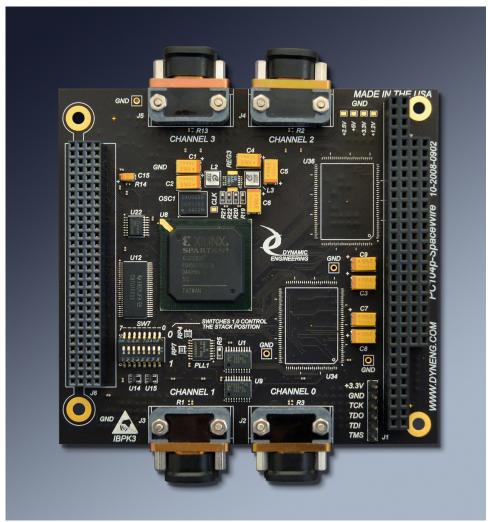

Corresponding Hardware: 10-2008-09(04)

## SpaceWireBK PMC, PCIe, PCI, PC104p versions

Four-Channel SpaceWire Interface

Dynamic Engineering 150 DuBois St., Suite B&C Santa Cruz, CA 95060 (831) 457-8891

©2004-2024 by Dynamic Engineering. Other trademarks and registered trademarks are owned by their respective manufacturers. Revised 3/7/2024 This document contains information of proprietary interest to Dynamic Engineering. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to ensure that this manual is accurate and complete. Still, the company reserves the right to make improvements or changes in the product described in this document at any time and without notice. Furthermore, Dynamic Engineering assumes no liability arising out of the application or use of the device described herein.

The electronic equipment described herein generates, uses, and can radiate radio frequency energy. Operation of this equipment in a residential area is likely to cause radio interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

Connection of incompatible hardware is likely to cause serious damage.

### **Table of Contents**

| PRODUCT DESCRIPTION                                             | 8        |

|-----------------------------------------------------------------|----------|

| THEORY OF OPERATION                                             | 14       |

| PROGRAMMING                                                     | 19       |

| Register Definitions                                            | 23       |

| SPWR_BASE_CNTL                                                  | 23       |

| SPWR_USER_SWITCH                                                | 25       |

| SPWR_TIME_CNTRL                                                 | 27       |

| SPWR_TIME_COUNT                                                 | 28       |

| SPWR_PLL_FIFO                                                   | 29       |

| SPWR_PLL_STATUS                                                 | 29       |

| SPWR_CHAN_CNTRL_0-3                                             | 31       |

| SPWR_CHAN_STATUS_0-3                                            | 35       |

| SPWR_CHAN_FIFO_0-3                                              | 39       |

| SPWR_CHAN_WR_DMA_PNTR_0-3                                       | 39       |

| SPWR_CHAN_TX_FIFO_COUNT_0-3                                     | 41       |

| SPWR_CHAN_RD_DMA_PNTR_0-3                                       | 42       |

| SPWR_CHAN_RX_FIFO_COUNT_0-3                                     | 43       |

| SPWR_CHAN_TX_PKT_LEN_0-3                                        | 44       |

| SPWR_CHAN_RX_PKT_LEN_0-3                                        | 44       |

| SPWR_CHAN_TX_AMT_0-3                                            | 45       |

| SPWR_CHAN_RX_AFL_0-3                                            | 45       |

| SPWR_CHAN_CREDIT_AND_TIMECODE_STATUS_0-3                        | 46       |

| SPWR_CHAN_RX_PKT_FF_FULL_CNTRL_0-3 SPWR_CHAN_TX_DDR_FIFO_CNT0-3 | 47<br>48 |

| SPWR_CHAN_TX_DDR_FIFO_CNT0-3 SPWR_CHAN_RX_DDR_FIFO_CNT0-3       | 48       |

| SPWR_CHAN_RX_DDR_FIFO_CN10-3<br>SPWR_CHAN_BURSTIN_PTR0-3        | 48       |

| SPWR CHAN BURSTOUT PTR0-3                                       | 49       |

| SPWR CHAN TX STRT ADD0-3                                        | 50       |

| SPWR_CHAN_TX_STOP_ADD0-3                                        | 50       |

| SPWR_CHAN_RX_STRT_ADD0-3                                        | 50       |

| SPWR CHAN RX STOP ADD0-3                                        | 51       |

| SI WK_CHAN_KA_STOL_ADD0-3                                       | 51       |

| (CC)PMC (PCI) PN1 INTERFACE PIN ASSIGNMENT                      | 53       |

| (CC)PMC (PCI) PN2 INTERFACE PIN ASSIGNMENT                      | 54       |

| (CC)PMC PN4 USER INTERFACE PIN ASSIGNMENT                       | 55       |

**Embedded Solutions**

| APPLICATIONS GUIDE           | 56 |

|------------------------------|----|

| Interfacing                  | 56 |

| CONSTRUCTION AND RELIABILITY | 57 |

| THERMAL CONSIDERATIONS       | 58 |

| WARRANTY AND REPAIR          | 58 |

| Service Policy               | 58 |

| Out of Warranty Repairs      | 58 |

| For Service Contact:         | 58 |

| SPECIFICATIONS               | 59 |

| ORDER INFORMATION            | 61 |

# List of Figures

| FIGURE 1  | SPACEWIRE BK BLOCK DIAGRAM                            | 9  |

|-----------|-------------------------------------------------------|----|

| FIGURE 2  | SPACEWIRE BK DDR BLOCK DIAGRAM                        | 10 |

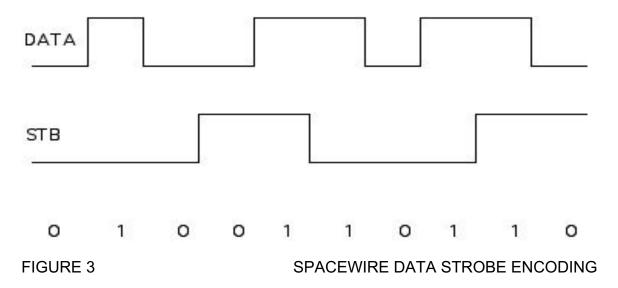

| FIGURE 3  | SPACEWIRE DATA STROBE ENCODING                        | 16 |

| FIGURE 4  | SPACEWIRE ADDRESS MAP                                 | 22 |

| FIGURE 5  | SPACEWIRE BASE CONTROL REGISTER                       | 23 |

| FIGURE 6  | SPACEWIRE USER SWITCH PORT                            | 25 |

| FIGURE 7  | SPACEWIRE TIME CONTROL REGISTER                       | 27 |

| FIGURE 8  | SPACEWIRE TIME COUNT REGISTER                         | 28 |

| FIGURE 9  | SPACEWIRE PLL DATA FIFO                               | 29 |

| FIGURE 10 | SPACEWIRE PLL STATUS REGISTER                         | 29 |

| FIGURE 11 | SPACEWIRE CHANNEL CONTROL REGISTER                    | 31 |

| FIGURE 12 | SPACEWIRE CHANNEL STATUS REGISTER                     | 35 |

| FIGURE 13 | SPACEWIRE CHANNEL RX/TX FIFO PORTS                    | 39 |

| FIGURE 14 | SPACEWIRE CHANNEL WRITE DMA POINTER PORT              | 39 |

| FIGURE 15 | SPACEWIRE CHANNEL TX FIFO DATA COUNT PORT             | 41 |

| FIGURE 16 | SPACEWIRE CHANNEL READ DMA POINTER PORT               | 42 |

| FIGURE 17 | SPACEWIRE CHANNEL RX FIFO DATA COUNT PORT             | 43 |

| FIGURE 18 | SPACEWIRE TX PACKET LENGTH FIFO PORTS                 | 44 |

| FIGURE 19 | SPACEWIRE RX PACKET LENGTH FIFO PORTS                 | 44 |

| FIGURE 20 | SPACEWIRE CHANNEL TX ALMOST EMPTY LEVEL REGISTER      | 45 |

| FIGURE 21 | SPACEWIRE CHANNEL RX ALMOST FULL LEVEL REGISTER       | 45 |

| FIGURE 22 | SPACEWIRE CHANNEL TIMECODE AND CREDIT STATUS REGISTER | 46 |

| FIGURE 23 |                                                       | 47 |

|           | SPACEWIRE CHANNEL TX DDR FIFO COUNT                   | 48 |

|           | SPACEWIRE CHANNEL RX DDR FIFO COUNT                   | 48 |

|           | SPACEWIRE CHANNEL TX DDR CURRENT PTR                  | 49 |

| FIGURE 27 |                                                       | 49 |

|           | SPACEWIRE CHANNEL TX DDR START ADDRESS                | 50 |

|           | SPACEWIRE CHANNEL TX DDR STOP ADDRESS                 | 50 |

|           | SPACEWIRE CHANNEL RX DDR START ADDRESS                | 50 |

| FIGURE 31 | SPACEWIRE CHANNEL RX DDR STOP ADDRESS                 | 51 |

| FIGURE 32 | MDM I/O CONNECTOR PINOUTS                             | 52 |

| FIGURE 33 | (CC)PMC-SPACEWIRE PN1 INTERFACE                       | 53 |

| FIGURE 34 | (CC)PMC-SPACEWIRE PN2 INTERFACE                       | 54 |

| FIGURE 35 | (CC)PMC-SPACEWIRE PN4 INTERFACE                       | 55 |

Embedded Solutions

#### **Product Description**

SpaceWire is part of the Dynamic Engineering family of modular I/O. This manual describes the "BK" family of SpaceWire. Currently PCIe, PCI, PC104p, and PMC versions are available. Please refer to the K family manual for information about the original memory map models.

Each has identical functionality with some variation in the IO connectors. Four ports are supported per card, each with internal FIFO and separate DMA engines to support high speed operation.

To receive the newer version covered in this manual add "-BK" to the part number.

K refers to the last planned update to the original SpaceWire design. Beyond K "BK" is the new version. Since the original PN is called out in client documentation and since the BK version has an updated memory map Dynamic Engineering decided to require the –BK addition to the PN to avoid mistakes in ordering.

External FIFOs can be installed for additional storage capability. Options are available to have the external FIFO attached to channel 0 RX and TX or channels 0 and 1 RX only.

DDR is being added to the designs with the PCIe and PC104p models having this feature incorporated.

Revision 04 and later PCI-SpaceWire fab required for BK Revision 08 and later PMC-SpaceWire fab required for BK Revision 01 and later PCIe-SpaceWire fab required for BK

Revision 04 and later PCIe-SpaceWire PCB required for BK with DDR.

#### Additional features of BK models:

- 1. Larger 16Kx32 FIFOs for Rx and Tx data storage per channel

- 2. Updated PLL programming interface

- 3. Updated memory map to allow for additional features

- 4. Expanded Time Code time base 32 bits instead of 20

- 5. Larger possible segment size for DMA.

- 6. 200 MHz operation 70C [PLL output is limited to 166 MHz for 85C]

- 7. Industrial Temperature components

- 8. Big Endian lane swapping for DMA transfers selectable option in SW.

- 9. DDR models have 128Mx16 allocated 8Mx32 per port.

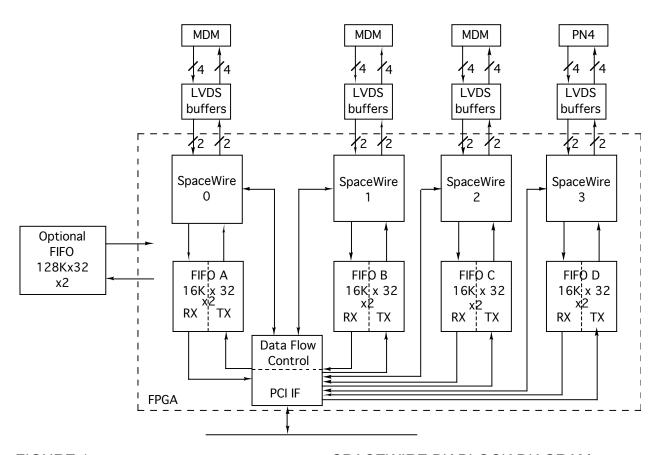

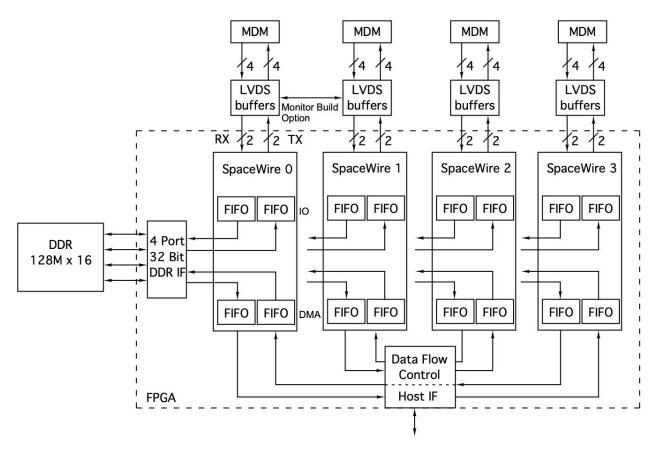

The following diagram shows the "BK" SpaceWire configuration (non-DDR versions):

FIGURE 1

SPACEWIRE BK BLOCK DIAGRAM

Note: Figure 1 and 2 do not show the Packet FIFOs which are 1K x 32 per channel per direction [8] to store packet sizes for transmission or definitions from reception-and the PLL support FIFOs and/programming engine.

The following diagram shows the "BK" SpaceWire configuration (DDR versions):

FIGURE 2

SPACEWIRE BK DDR BLOCK DIAGRAM

The port 3 connector implementation varies depending on the format. The PMC version can be configured with 3 MDM connectors, and have 1 channel on Pn4 or all 4 channels routed to Pn4. In all cases, high speed, differential routing with controlled impedance and matched lengths are used for the SpaceWire signaling. It is recommended to use a SpaceWire compatible cable to interconnect your hardware. Dynamic Engineering has several standard lengths of cable and offers custom lengths as well. <a href="https://www.dyneng.com/SpaceWireCable.html">https://www.dyneng.com/SpaceWireCable.html</a>

If you can use the SpaceWire hardware set but need an alternate protocol please contact Dynamic Engineering. We will redesign the state machines and create a custom interface protocol. See our web page for current protocols offered. Please contact Dynamic Engineering with your custom application.

The SpaceWire protocol implemented provides Low Voltage Differential Signaling (LVDS) data inputs and outputs. The transmit data rate is selected by a combination of the programmed output frequencies of the PLL and the divisor values in the channel control registers. The PLL is programmed via software over a serial I2C interface. Transmit data rates are selectable from 2 Mbps to 200 Mbps. The receiver will automatically adjust to the data rate seen.

The SpaceWire specification requires that the transmit frequency be 10 Mbps during the link connection process. In order to accommodate this, the PLL frequency should be at least close to a multiple of 10 MHz. Once the link protocol has established a connection, the transmit speed will convert to the desired transmit rate specified in the channel control registers.

Four independent SpaceWire ports are provided per card. Each SpaceWire port has two LVDS signal pairs for input and two LVDS signal pairs for output. The electrical interface for SpaceWire is as specified in document ECSS-E-50-12C, published by the European Cooperation for Space Standardization dated 31 July 2008. Connections for the first three/four SpaceWire ports on the card are with MDM style connectors as required by the specification.

For PMC and XMC devices the bezel restricts the number of ports at the bezel. The 4<sup>th</sup> port is presented on the rear IO. Any or all of the four ports can be routed to the rear IO connector rather than the MDM connectors. Isolation and stub control is provided by  $0\Omega$  jumpers.

PMC-SpaceWire uses a 10 mm inter-board spacing for the front panel, standoffs, and PMC connectors. The 10 mm height is the "standard" height and will work in most systems with most carriers. If your carrier has non-standard connectors (height) to mate with the PMC-SpaceWire, please let us know. We may be able to do a special build with a different height connector to compensate.

All formats available and planned will have a common software interface allowing for porting between systems. Dynamic Engineering offers drivers and reference software for Windows®, Linux, and VxWorks.

Each SpaceWire channel is supported by two 16K by 32-bit FIFOs. The TX FIFOs support long-word writes and the RX FIFOs support long-word reads. For testing, a FIFO test bit in each channel control register enables the data to be routed from the TX to the RX FIFO for a full 32-bit path. DMA operation is supported in both test and operational modes.

DDR models have different configuration with 4 smaller 1Kx32 FIFOs to handle the immediate IO and DMA requirements with the DDR path between them. When the loop-back mode is enabled, the TX IO FIFO is looped back to the RX IO FIFO. Tx DMA FIFO => DDR => TX IO FIFO => RX IO FIFO => DDR => RX DMA FIFO is the resulting path.

The DDR segments are allocated within the same device using different memory ranges. The ranges default to provide the same amount of memory to each port. The allocations are programmable. By having the default values, the HW will operate properly without the need to change user SW. See the memory/bit map section for more information.

The DDR operates at a much higher frequency and can easily keep up with the port traffic. There is the possibility of some latency, the rate matching buffers cure this plus provide the rate matching.

Each SpaceWire port can receive SpaceWire packets and store them in the associated IO FIFOs. Each SpaceWire packet will be zero extended to align with 32-bit long words. The actual number of bytes in the packet will be stored in the RX packet-length FIFO [1Kx32] and the Data is stored in the IO FIFO.

The host can poll the FIFO flags or wait for the packet received or RX almost full interrupts. The packet data can be read by the host directly from the RX data FIFO [target or DMA]. All models have hardware implemented flow control using the SpaceWire FCT count to prevent overflow into either the Data or Packet FIFOs automatically.

Each SpaceWire transmit port has a separate TX IO FIFO. The FIFO is written as long words. The number of bytes to be transmitted is specified by writing a byte count to the TX packet-length FIFO [1Kx32]. Provided the connection is established, and the flow control from the destination side has authorized data transfer; whenever TX data and packet-length values are written, the transmitter will send data. A packet disable bit in the channel control register allows the interface to function without packetizing the data. When in this mode the transmitter will send data as soon as it is written to the TX FIFO. This essentially treats the data as one infinite length packet.

More on byte alignment: Transmit bytes are read from byte positions 0->3 byte lane wise [7-0] first, [15-8] second, [23-16] third and [31-24] last and the bytes are transmitted in this order. For message byte-counts not divisible by four, the last longword is read as described. Any unused bytes are considered padding with the next message starting with the next FIFO long-word. For example, with 7 bytes to send, a word of 4 bytes will be read, then the lower 3 bytes will be read and sent and the 8<sup>th</sup> byte will be dropped.

In the receive direction the action is similar. Bytes are written as long-words to the RX FIFO. The first byte received is loaded into long-word byte 0 [7-0], then byte 1 [15-8], byte 2 [23-16] and byte 3 [31-24]. Whenever a message does not have a complete long-word to load and the end-of-packet character is received, zero-padding of the unused upper-bytes will occur before the long-word is written to the FIFO.

The SpaceWire design supports interrupts. An interrupt can be configured to occur when the TX FIFO is almost empty, the RX FIFO is almost full, when a SpaceWire packet has been transmitted or received, when a time-code character is received or when an error has occurred. All interrupts are individually maskable, and a channel master interrupt enable is provided to disable all interrupts on a channel simultaneously. The current real-time status is also available from the FIFOs making it possible to operate in a polled mode.

For Command & Control situations direct read-write access to the FIFOs makes sense. The messages tend to be short and the added overhead of setting up DMA is not justified. For data transfer DMA is recommended. Each channel has a separate transmit and receive DMA engine for a total of 8 programmable units. The DMA engines can be programmed for long transfers and handle scatter-gather requirements automatically. With only 1 interrupt to deal with at the end of the transfer it is the lowest overhead transfer method for medium and large transfers. Internal to the design is an 8-channel DMA arbiter which controls which port can access the bus for DMA operation. The arbiter operation is completely automatic.

#### **Theory of Operation**

SpaceWire designs are for transferring data from one point to another using the SpaceWire protocol as specified in document ECSS-E-50-12C, published by the European Cooperation for Space Standardization dated 31 July 2008.

Continuous development in the SpaceWire community means fairly frequent updates for new features. Generally new features can be added to a released card with a FLASH update. New features are designed to allow for non-updated software to still function – please set undefined bits to zero when programming to facilitate the migration path.

The BK series SpaceWire board(s) feature a Xilinx FPGA. The FPGA contains the PCI interface, all of the registers, FIFO's and protocol controlling elements of the SpaceWire design. Only the transceivers and clock circuitry are external to the Xilinx device.

A logic block within the FPGA controls the PCI interface to the host CPU. The SpaceWire design requires one wait state for read or writes cycles to any address. The wait states refer to the number of clocks after the PCI-core decode before the "terminate with data" state is reached. Two additional clock periods account for the 1 clock delay to decode the signals from the PCI bus and to convert the terminate-with-data state into the TRDY signal.

Scatter-gather DMA is provided in this design. Once the physical address of the first chaining descriptor is written to the DMA pointer register, the interface will read a 12-byte block from this location. The first four bytes comprise a long-word indicating the physical address of the first block of the IO buffer passed to the read or write call. The next four bytes represent a long-word indicating the length of that block. The final four bytes are a long-word indicating the physical address of the next chaining descriptor along with two flag bits, in bit position 0 and 1. Bit zero is set to one if this descriptor is the last in the chain. Bit one is set to one if the IO transfer is from the SpaceWire board to host memory, and zero if the transfer is from memory to the board. These bits are then replaced with zeros to determine the address of the next descriptor, if there is one.

<u>NOTE</u>: The direction bit (bit 1) must be set when the physical address of the first chaining descriptor is written to the DMA pointer register (read DMAs only) or a DMA error will result.

The eight DMA controllers obtain access to the PCI bus by asserting a request to the DMA arbiter. Once a controller is granted PCI access, it keeps the bus until it drops its request. At this point if another controller is requesting the bus, it will be granted access. If multiple DMA controllers are asserting requests, the arbiter grants access in a round-robin pattern.

A controller will drop request when it reaches the end of a scatter-gather list entry or the end of a DMA descriptor acquisition. It will also drop request when a transfer from the device to memory is almost out of data, or when a transfer from memory to the device is almost out of room to store the data, or if it has held the PCI bus for 1024 PCI clocks.

A retry counter is included in the DMA controllers. This counter is incremented whenever the DMA controller initiates a PCI bus-cycle and is cleared whenever the controller drops bus request or a data-word is successfully transferred. If the count reaches 1024, the controller is forced to drop bus request, which allows another controller to gain access. The purpose of the retry counter is to prevent a DMA controller from hanging-onto the PCI bus at the detriment of the other ports.

Several state-machines within the FPGA control the link, FIFOs, data transceivers, and flow-control for each channel. The transmitter and receiver for each channel are interdependent. The transmitter requires flow-control information from the receiver to function and the receiver requires the transmitter to send flow-control tokens to regulate the flow of received data.

In a typical transmit sequence the local receiver receives flow control tokens (FCTs) from the remote node. Each FCT authorizes the local transmitter to send eight N(ormal)-Chars (a data-byte, End-Of-Packet token (EOP) or Error End-of-Packet (EEP)) back to the remote node. An up-down counter is used to keep track of the number of N-Chars authorized, and the number of N-Chars that have been sent. Likewise, the local transmitter sends FCTs to the remote receiver node to enable that node's transmitter to send N-Chars to the local receiver. The number of outstanding FCTs is based on the amount of room available in the receive FIFO with an upper limit of 7 FCTs (56 bytes).

The transmitters will multiplex Time-Code characters, FCT characters, N-characters and NULL characters (in that order of priority) onto the data stream to regulate the flow of data in both directions. At the end of a transmitted packet, the transmitter will append an EOP (or possibly an EEP if relaying a packet with an error) character to the message stream to alert the receiver to the completion of the current packet.

The SpaceWire design uses Data-Strobe encoding where clock and data information are sent on two paired serial links. Exactly one transition occurs in either the data line or the strobe line at the end of each bit period allowing the clock to be recovered from the data strobe pair. The timing is shown in figure 2.

Note: SpaceFiber uses a similar mechanism but with 8B10B encoding.

Before the transmitter can start operation, it must establish a link with the connected node. When the link enable control bit is set, the connection state-machine resets the NULL-detected latch and waits 6.4 microseconds before enabling the receiver. The receiver then monitors SpaceWire link activity for 12.8 microseconds. If any link errors or tokens other than NULLs are seen during this period, the receiver is disabled and the process starts over.

At this point the state-machine is in the ready state waiting for a start or auto-start control bit to be set to move to the starting state. The start control bit causes the transmitter to immediately begin sending NULLs and the receiver to look for a NULL in response, whereas the auto-start control bit causes the state-machine to wait for a NULL to be received before transitioning to the starting state and sending NULLs. If a NULL is not seen within 12.8 microseconds while in the starting state, or if errors or tokens other than NULLs are seen, the transmitter and receiver are disabled and the process starts over.

When the transmitter has sent a NULL and the receiver has received a NULL character, the transmitter sends an FCT character and the receiver looks for an FCT in return. If this occurs, it means that the remote node has recognized the NULL and is ready to connect. Once an FCT has been sent and received the link proceeds to the run state.

The transmit frequency is then switched to the requested operational frequency from the 10 MHz connection frequency and Time-codes, FCTs and N-chars (data or end-of-packet tokens) can be sent to and from the node. (See figure 8-2: State diagram for SpaceWire link interface on page 64 of the SpaceWire spec. ECSS-E-ST-50-12C)

The SpaceWire specification allows for a maximum of 56 bytes of credit (seven FCTs) to be outstanding at any time. For each eight bytes that are received, the receiver will request the transmitter to send another FCT as long as sufficient buffer space exists to accommodate the additional data. If the receiver receives a data byte when the outstanding credit is zero, or if an FCT is received that causes the transmit credit to exceed 56 bytes, a credit error has occurred.

The credit error is one of several error conditions that can disrupt the link connection. The others include parity error, disconnect error and escape error. If any of these occur a receive error and the offending error condition status will be latched, the link will disconnect and after a delay, attempt to re-establish the connection.

The parity error occurs when the relevant bits of two successive characters do not constitute odd parity (an odd number of ones). Parity coverage for SpaceWire is offset from the character boundaries by two bits. Although each character begins with a parity bit followed by a data control flag, these two bits are combined with the payload bits from the previous character to determine the parity. The disconnect error occurs when there is no activity on the strobe or data lines to the receiver for a period of 850 nanoseconds. The escape error occurs when an escape character is followed by anything other than an FCT or a data character.

Beginning with Flash Rev 02 STD minor rev 8, 128 & 128RX minor rev5, a Receive Packet FIFO control register was added to select when to back pressure the link to prevent receive packet FIFO overflows from occurring. This improvement effectively removes a SW race condition for small packets<sup>1</sup>. The register can be set to 0x3FF or

If the controlling processor does not keep up with the Packet received interrupts the Packet FIFO would overflow and descriptors lost. The HW update adds the Packet FIFO status to the FCT calculations to prevent overflow.

0x000 to operate in legacy mode. A receive FIFO overflow will also cause a receive error to be latched, but will not in itself cause a link disconnect.

If a receive data-packet is in progress when an error occurs, the receiver ceases writing data to the receive data FIFO and writes the receive packet-length FIFO with the current byte-count with the packet error bit set. If this packet fragment is to be relayed to a remote node, it should be terminated with an EEP rather than an EOP.

If a transmit packet was in progress when the error occurred, the transmitter stops sending data and attempts to purge the remainder of the current packet from the transmit FIFO. Data must be read from the FIFO at the rate of 132 bytes per microsecond, rather than using the FIFO reset, to avoid deleting data belonging to subsequent packets.

A 30 microsecond delay is provided for this purpose, however, if the packet-length is large or if all the packet data is not currently present in the transmit FIFO, the transmitter will be unable to complete the data purge within the 30 microsecond period and the link state-machine will go ahead and disable the receiver and transmitter in preparation for reestablishing the link. The remote receiver that is receiving the data will detect an error when the link is disabled, if it has not already, and will be aware that the packet has been prematurely terminated.

This will clear the transmitter and receiver error state, but a transmitter purge error status bit will be latched to alert the user of this error condition. The user can then read the transmit packet-length FIFO count to determine how many packets are pending, reset the transmit FIFO (which also clears the transmit packet-length FIFO) and perform whatever error recovery is indicated.

See the SpaceWire specification for clarification or elaboration on any of these features.

#### **Programming**

Programming the SpaceWire design requires only the ability to read and write data from the host. The base address is determined during system configuration of the PCI bus. The base address refers to the first user address for the slot in which the board is installed. The Vendorld = 0xDCBA. The CardId = 0x0055.

Depending on the software environment it may be necessary to set-up the system software with the SpaceWire "registration" data.

If DMA is used it may be necessary to acquire a block of non-paged memory that is accessible from the PCI bus in which to store chaining descriptor list entries. If the Dynamic Engineering device drivers are used, the I/O channel driver will handle all the DMA internal mechanics automatically.

In order to transfer data to another SpaceWire node, several steps must be performed. First a physical connection must be established with the appropriate interface cable. Then the PLL must be programmed to the desired clock configuration. The PLL is connected to the FPGA by an I<sup>2</sup>C serial bus. The PLL internal registers are loaded with 40 bytes of data that are derived from a .jed file that can be generated by the CyberClock utility from Cypress semiconductor.

Reference: <a href="https://www.dyneng.com/\_Download/Utilities/CyberClocks.zip">https://www.dyneng.com/\_Download/Utilities/CyberClocks.zip</a>. Select CyClocksRT; the specific PLL part number is CY22393; and the external reference clock frequency is 40 MHz. You can specify frequencies for CLKA – CLKD which supply the I/O reference clocks for channels 0 – 3 respectively. Click the Calculate button and save the file. Newer versions of this utility may be available from Infineon/Cypress.

The SpaceWire card is populated with industrial temperature components. If operating in the Industrial temperature range be sure to set the proper temperature in the CyberClocks software. The upper frequency of the PLL is somewhat limited in Industrial temperature mode. If using for commercial temperature applications, select the commercial temperature range setting to allow for higher operating frequencies.

A four-bit count field in each channel's control register allows the I/O reference clock to be divided by any integer value from 1 to 16 (count values 0-0xF) to yield the final operational bit-rate. There is a 5-bit initial count field for each channel in the base control register that is used to divide the I/O reference clock in order to generate the ~10 Mbit per second connection rate. To allow the channels to achieve this connection rate, the PLL should not be programmed to frequencies below 10 MHz and should be at least close to a multiple of 10 MHz.

Routines to program the PLL are included in the driver and UserApp code provided in the engineering kit for the board. The driver will analyze the 40-byte PLL register field to determine the requested frequencies and set the initial count values automatically whenever the PLL is reprogrammed. If you are writing your own driver, contact Dynamic Engineering and we can send you a file with code excerpts from our driver and test software that cover each step of the process.

The link Enable bit and either the Start or Auto-start bit must be set in the channel control register along with the desired operational clock divisor and any interrupt enables that are to be monitored. When the link has been established as reported in the channel status register, data may be written to the transmit FIFO using either singleword writes or DMA. If the packet disable bit has been set, data will be sent as soon as it is written, provided that the receiving node has authorized the transfer. In this mode the data is treated as a single infinite-length packet.

If packetizing is not disabled, the data will not be sent until a packet-length has been written to the SPWR\_CHAN\_TX\_PKT\_LEN FIFO. If the packet-length is not divisible by four, the remainder of the last 32-bit FIFO word will be ignored and the next packet's data will begin with the next FIFO word. A packet-length must be written for each packet to be sent, unless the constant packet-length control bit is set. If this bit is set, the first packet-length read will be used continuously until either the data in the transmit data FIFO is exhausted or the constant packet-length control bit is cleared.

Once the link has been established, the receiver will automatically adapt to the frequency of the remote node's transmitter. As data is received, a 32-bit data word will be written to the receive FIFO for every four bytes that are received. When an end-of-packet character is received, the remainder of the received data will be written to the FIFO regardless of whether four bytes have been received (the unused bytes are written as zeros) and the received packet-length (byte count) will be written to the SPWR\_CHAN\_RX\_PKT\_LEN FIFO. The packet done bit will also be set and an interrupt generated, if it has been enabled.

#### **Firmware Updates**

Revision A: First release of BK. See feature table for new features. 8/14

Revision B1: Second release of BK. Updated for new FPGA pinout, external clock recovery, PMC rear IO connector redefined to match ccPMC version. Add lane steering for DMA in Big Endian systems. 3/16/15

Revision B2: minor update for better internal timing 12/15

Revision B2: -128 original release based on B2 version standard product.

Revision B3-5: 9/2016 Fine tuning of FPGA terminations and timing based on new layout with built in clock offset for improved hold time. Added minor revision field to status.

Switch to numerical revisions

Revision 02p8 STD, 02p5 128 & 128RX: Implemented Receive Packet FIFO control register and logic to each channel. Changed PCI bus access logic, FIFO Full logic, and added timer to prevent bus lockups. Drivers changed TSI 384 bridge settings to prevent cache coherency issue in certain system configurations. Added Channel Credit & Time Code Status register to each channel.

Revision 10p1 CreateType 4 with DDR added, FIFO option removed. 2/29/24 [completed FAI]

#### Address Map

| Addi 633 Map                  |                                                                    |

|-------------------------------|--------------------------------------------------------------------|

| Register Name                 | Offset Description                                                 |

| SPWR BASE CNTRL               | 0x0000 // 0 Base control register                                  |

| SPWR USER SWITCH              | 0x0004 // 1 User switch & status read port                         |

| SPWR TIME CNTRL               | 0x0008 // 2 Time control register                                  |

| SPWR TIME COUNT               | 0x000C// 3 Time Code update rate                                   |

| SPWR PLL FIFO                 | 0x0010 // 4 Write to PLL programming FIFO, Read PLL read-back FIFO |

| SPWR_PLL_STATUS               | 0x0014 // 5 Status associated with PLL programming                 |

| SPWR CHAN CNTRL               | 0x0000 // 0 Control register                                       |

| SPWR CHAN STATUS              | 0x0004 // 1 Status register                                        |

| SPWR CHAN FIFO                | 0x0008 // 2 TX/RX FIFOs single word access                         |

| SPWR_CHAN_WR_DMA_PNTR         | 0x000C // 3 write DMA physical PCI dpr address                     |

| SPWR CHAN TX FIFO COUNT       | 0x000C // 3 transmit FIFO data count                               |

| SPWR CHAN RD DMA PNTR         | 0x0010 // 4 read DMA physical PCI dpr address                      |

| SPWR_CHAN_RX_FIFO_COUNT       | 0x0010 // 4 receive FIFO data count                                |

| SPWR_CHAN_TX/RX_PKT_LEN       | 0x0014 // 5 Write TX/Read RX packet-length                         |

| SPWR CHAN TX AMT              | 0x0018 // 6 TX almost empty level                                  |

| SPWR_CHAN_RX_AFL              | 0x001C // 7 RX almost full level                                   |

| SPWR_CHAN_CREDIT_TC_STATUS    | 0x0020 // 8 Credit and TimeCode Status register                    |

| SPWR_CHAN_RX_PKT_FF_FULL_CNTL | 0x0024 // 9 RX Packet FIFO Full Control register                   |

| Type 4 models only            |                                                                    |

| SPWR_CHAN_TX_DDR_FIFO_CNT     | 0x0028 // 10 Tx FIFO count including DDR                           |

| SPWR_CHAN_RX_DDR_FIFO_CNT     | 0x002C // 11 Rx FIFO count including DDR                           |

| SPWR_CHAN_BURST_IN_PTR        | 0x0030 // 12 Tx DMA Current Pointer                                |

| SPWR_CHAN_BURST_OUT_PTR       | 0x0034 // 13 Rx DMA Current Pointer                                |

| SPWR_CHAN_TX_STRT_ADD         | 0x0038 // 14 Tx Start Address – DDR allocation                     |

| SPWR_CHAN_TX_STOP_ADD         | 0x003C // 15 Tx Stop Address – DDR allocation                      |

| SPWR_CHAN_RX_STRT_ADD         | 0x0040 // 14 Rx Start Address – DDR allocation                     |

| SPWR_CHAN_RX_STOP_ADD         | 0x0044 // 15 Rx Stop Address – DDR allocation                      |

|                               |                                                                    |

#### FIGURE 4

#### SPACEWIRE ADDRESS MAP

Channel definitions repeat. Each port having the internal offsets shown plus the following table. All are relative the assigned BAR0 address.

Port 0 0x050

Port 1 0x0A0

Port 2 0x0F0

Port 3 0x140

#### **Register Definitions**

#### SPWR\_BASE\_CNTL

[0x0000] Base Control Register (read/write)

| Base Control Register                              |                                                            |                                                                                                                                                                                             |

|----------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3°<br>30<br>29<br>27<br>22<br>22<br>22<br>20<br>19 | 0<br>9-28<br>7-25<br>4<br>3<br>2<br>1<br>0<br>9-15<br>4-10 | Description BigEndianDma loRst Time-Code Control Flags Spare PLL USE ALT PLL CHK PLL RD PLL RST PLL Enable IO Clock D Initial Divisor IO Clock B Initial Divisor IO Clock A Initial Divisor |

#### FIGURE 5

#### SPACEWIRE BASE CONTROL REGISTER

All bits are active high and are reset on system power-up or reset, except PLL enable, which defaults to enabled (high) on power-up or reset.

IO Clock A-D Initial Divisor: These four fields determine the divisor used to generate the 10 MHz connection clock rate. IO clock A is used for channel 0, IO clock B is used for channel 1, IO clock C is used for channel 2 and IO clock D is used for channel 3. Depending on the frequencies programmed into the PLL, different divisors are required to achieve the 10 MHz bit-rate required by the SpaceWire specification for establishing the link connection. These fields specify those divisors. The frequency divisor is actually one more than the value entered. A value of zero corresponds to a divisor of one. A value of one corresponds to a divisor of two etc. If the Dynamic Engineering device driver is used, these values are written automatically when the PLL is programmed.

<u>PLL Enable</u>: When this bit is set to a one, the signals used to program and read the PLL are enabled.

PLL RST: When Set '1' causes a reset to the PLL programming HW.

<u>PLL RD:</u> when set selects reading the PLL, when cleared selects writing to the PLL registers.

PLL CHK: Set to check PLL address.

PLL USE ALT: When set selects the Alternate PLL address.  $0 \Rightarrow x69, 1 \Rightarrow x6A$

<u>Time-Code Control Flags</u>: These two bits are added to the six-bit time count in bit positions 7 and 6. Their purpose is currently not defined in the SpaceWire specification.

loRst when '1' causes a reset to the DDR controller for each of the 4 ports. Separate port only resets are available within the port. '0' for normal operation.

BigEndianDma: '0' disables this option. '1' enables this option. When operating with a Big Endian platform and using PCI accesses DMA can have challenges. The register accesses directly over the PCI bus are usually taken care of automatically with byte swapping within the CPU or PCI interface on the CPU. DMA data is written to or read from the local memory and is not swapped. The direct read/write from memory ends up with scrambled data [relative to SpaceWire little endian definitions]. Setting this bit will byte reverse the data for the DMA path into the Tx and out of the Rx FIFO's only. Register accesses are not affected.

31-24, 23-16, 15-8, 7-0 ⇔ 7-0, 15-8, 23-16, 31-24 byte swapping pattern implemented.

#### SPWR USER SWITCH

[0x0004] User Switch Port - read only

| İ | Dipswitch Port |                                                       |  |

|---|----------------|-------------------------------------------------------|--|

|   | Data Bit       | Description                                           |  |

|   | 31             | Calibration Done                                      |  |

|   | 30-28<br>27    | Spare Channel 3 Interrupt Active                      |  |

|   | 26             | Channel 3 Interrupt Active Channel 2 Interrupt Active |  |

|   | 25             | Channel 1 Interrupt Active                            |  |

|   | 24             | Channel 0 Interrupt Active                            |  |

|   | 23-20          | Xilinx Design Revision Minor                          |  |

|   | 19-16          | Xilinx Design Configuration Type                      |  |

|   | 15-8           | Xilinx Design Revision Number Major                   |  |

|   | 7-0            | Switch Setting                                        |  |

#### FIGURE 6

#### SPACEWIRE USER SWITCH PORT

Switch 7-0: The user switch is read through this port. The bits are read as the lowest byte. Access the read-only port as a long word and mask off the undefined bits. The dip-switch positions are defined in the silkscreen. For example, the switch figure below indicates a 0x12.

<u>Channel 0-3 Interrupt Active</u>: When a one is read, it indicates that the corresponding channel's interrupt is active. When a zero is read, that interrupt is inactive.

Calibration Done: on models with DDR this bit indicates the DDR initialization process has completed successfully. Also note the blinking LED indicating the DDR clock controller is locked onto the reference and supplying the required high speed clock outputs.

Xilinx Design Configuration Type Major and Minor and Xilinx Design Revision Number: These values of the describe the channel configuration and revision of the Xilinx design.

Currently there are 4 configurations for the HW with the following definitions note: as the DDR update is added to the form factors supported and current stock is depleted the DDR model will be shipped to all orders. In the meantime if your design requires the DDR type please ask for it.

0 => Spare

- 1 => S6 with internal 64 Kbyte data FIFOs and Two G byte maximum packet-lengths for all channels.

- 2 => S6 with internal 64 Kbyte data FIFOs and Two G byte maximum packet-lengths for all channels.

Plus external 128Kx32 FIFO's on for Channel 0 RX & Tx

- 3 => S6 with internal 64 Kbyte data FIFOs and Two G byte maximum packet-lengths for all channels.

Plus external 128Kx32 FIFO's on for Channel 0 & 1 RX.

- 4 => S6 with DDR plus 2, 1K FIFOs per path. Default of 32Mbytes per Rx or Tx port [DDR]. Miscellaneous enhancements to minimize latency and increase utility.

5-F => Spare

The Major Revision field is the released name for the particular revision. The Minor Revision field is for Dynamic Engineering revision tracking during development, and for minor released updates between Major Updates.

#### **SPWR TIME CNTRL**

[0x0008] Time Control Register (read/write)

| Time Control Register |                                    |  |

|-----------------------|------------------------------------|--|

| Data Bit              | Description                        |  |

| 31-15                 | Spare                              |  |

| 14-12                 | Channel 3 Time-Code Source Control |  |

| 11                    | Spare                              |  |

| 10-8                  | Channel 2 Time-Code Source Control |  |

| 7                     | Spare                              |  |

| 6-4                   | Channel 1 Time-Code Source Control |  |

| 3                     | Spare                              |  |

| 2-0                   | Channel 0 Time-Code Source Control |  |

#### FIGURE 7

#### SPACEWIRE TIME CONTROL REGISTER

All bits are active high and are reset to zero on system power-up or reset.

<u>Channel 0-3 Time-Code Source Control</u>: These four fields control the source of the time-code signals for the four channels as follows:

- "000"-> Disabled: Time-code characters are not sent by this channel.

- "001"-> Master: Time-code characters for this channel come from the master timer and time-code counter.

- "010"-> Channel 0: Time-code characters received by channel 0 are subsequently sent by this channel.

- "011"-> Channel 1: Time-code characters received by channel 1 are subsequently sent by this channel.

- "100"-> Channel 2: Time-code characters received by channel 2 are subsequently sent by this channel.

- "101"-> Channel 3: Time-code characters received by channel 3 are subsequently sent by this channel.

Write 0-5 to each of the fields to select the source for that channel. For example, writing the "101" pattern to channel 0 will have the time code received by channel 3 passed to channel 0 for retransmission. To use the local master use code "001" and so forth.

#### SPWR\_TIME\_COUNT

[0x000C] Time Count Register (read/write)

|                       | Time Control Register                         |

|-----------------------|-----------------------------------------------|

| <b>Data E</b><br>31-0 | <b>Description</b> Master Timer Divider Count |

FIGURE 8

SPACEWIRE TIME COUNT REGISTER

Master Timer Divider Count: This count is used to generate the TICK\_IN signal when a channel is used as the source for time-codes. The counter is clocked by the 80 MHz link clock and this count represents the count at which the counter resets to zero, increments the time-code and issues a TICK\_IN signal. If this field is set to zero, the six-bit time-code counter and the 32-bit tick timer are reset to zero; when the count is set to a non-zero value, counting proceeds. The 32-bit counter allows a maximum time between ticks of approximately 53.68 seconds.

Normally the timer is set to a much lower value, 1 mS for example. Program for N-1 to be exact since the count runs from 0-> programmed value and then back to 0.

#### SPWR PLL FIFO

[0x0010] PLL Data FIFO (read/write)

|                         | PLL Data FIFO                                   |

|-------------------------|-------------------------------------------------|

| <b>Data Bit</b><br>31-0 | <b>Description</b> Data to PLL or Data From PLL |

FIGURE 9

SPACEWIRE PLL DATA FIFO

SpaceWire has an improved I2C interface for programming the PLL. Dynamic Engineering driver support packages include utilities to take the .jed file from the Cypress CyberClocks program, parse and load into the FIFO with the proper sequence of controls via Base Control Register. Please see the reference code for the sequence. Linux, VxWorks, Win10/11 packages.

The data to program the PLL is written to this address. The hardware has a state-machine to read the data from the FIFO and load into the PLL. Similarly, the state-machine can read the data from the PLL and write it to the read side FIFO.

#### SPWR\_PLL\_STATUS

[0x0014] PLL Status (read/write)

| Time Control Register             |                                                                                                                                                                                    |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Bit 31-10 10 9 8 7 6 5 4 3 2 | Description Spare PLL Error Latched PLL Done Latched PLL Ready Spare PLL FIFO RX Data Valid PLL FIFO RX FULL PLL FIFO RX EMPTY Spare PLL FIFO TX Data Valid PLL FIFO TX Data Valid |  |

| 0                                 | PLL FIFO TX MT                                                                                                                                                                     |  |

FIGURE 10

SPACEWIRE PLL STATUS REGISTER

The PLL Status bits are used to as feed-back to control the transfer of data to and from the PLL FIFO. TX refers to programming the PLL and RX refers to reading back from the PLL.

The Latched Bits {10,9} are held until cleared by writing back with the bit position(s) set. Usually these bits are cleared before starting an operation.

PLL FIFO TX MT is set when the programming FIFO for the PLL is empty.

PLL FIFO TX FULL is set when the programming FIFO for the PLL is full.

<u>PLL FIFO TX Data Valid</u> is set when data is valid in the pipeline between the FIFO and the State –Machine. The bit is cleared each time the data is read. During operation this bit will toggle to provide some indication that the transfer is occurring.

PLL FIFO RX Empty is set when the read-back FIFO for the PLL is empty.

PLL FIFO RX FULL is set when the read-back FIFO for the PLL is full.

<u>PLL FIFO RX Data Valid</u> is set when Data is valid in the output port for the PLL read path. Data is pre-read from the FIFO and held in the FIFO holding register. The FIFO can be Empty and still have 1 word left in the holding register if Valid is still set.

<u>PLL Done Latch</u> is set when the transfer is completed. This bit can be polled to know when the PLL has been programmed or when the PLL has been read. Please note: The PLL settling time is in addition to the transfer time. Several mS should be delayed after programming the PLL to make sure the specified frequencies are within range. 10 mS is recommended.

<u>PLL Error Latched</u> is set when an error is detected in the I2C transfer. The main purpose for this bit is in discovery for the address of the PLL. The Address can be x6A or x69. Once the correct address is known this bit should be checked but not set. Sticky bit, write with bit position set to clear.

#### SPWR\_CHAN\_CNTRL\_0-3

[0x0050, 0x00A0, 0x00F0, 0x0140] Channel Control Register (read/write)

| Channel Control Register |                                         |

|--------------------------|-----------------------------------------|

| Data Bit                 | Description                             |

| 31                       | Read DMA Ready (read only)              |

| 30                       | Write DMA Ready (read only)             |

| 29-28                    | Time-Code Flags (read only)             |

| 27                       | DDR Disable for type 4.                 |

| 26                       | Spare                                   |

| 25                       | Return Valid Packet-Lengths Only Enable |

| 24                       | Transmit Packet-Length Repeat           |

| 23                       | Receive FIFO Programmable Level Load    |

| 22                       | Transmit FIFO Programmable Level Load   |

| 21                       | Read DMA Arbitration Priority Enable    |

| 20                       | Write DMA Arbitration Priority Enable   |

| 19                       | Read DMA Interrupt Enable               |

| 18                       | Write DMA Interrupt Enable              |

| 17                       | Force Interrupt                         |

| 16                       | Master Interrupt Enable                 |

| 15                       | Tick Received Interrupt Enable          |

| 14                       | Packet Received Interrupt Enable        |

| 13                       | RX Error Interrupt Enable               |

| 12                       | RX Almost Full Interrupt Enable         |

| 11                       | TX Almost Empty Interrupt Enable        |

| 10                       | Packet Disable                          |

| 9                        | Link Auto-Start                         |

| 8                        | Link Start                              |

| 7                        | Link Enable                             |

| 6                        | FIFO Loop-Back Enable                   |

| 5                        | Receive FIFO Reset                      |

| 4                        | Transmit FIFO Reset                     |

| 3-0                      | IO Clock Divisor                        |

|                          |                                         |

#### FIGURE 11

#### SPACEWIRE CHANNEL CONTROL REGISTER

All bits are active high and are reset on system power-up or reset.

<u>IO Clock Divisor</u>: This field determines the divisor used to generate the operational clock rate. The frequency divisor is actually one more than the value entered. A value of zero corresponds to a divisor of one, one corresponds to a divisor of two etc.

<u>Transmit/Receive FIFO Reset</u>: When one or both of these bits are set to a one, the corresponding data FIFO, packet-length FIFO and control and status circuitry will be reset. When these bits are zero, normal FIFO operation is enabled. FIFO resets are referenced to the PCI clock, two periods are required for proper reset.

<u>FIFO Loop-Back Enable</u>: When this bit is set to a one, any data written to the transmit FIFO will be immediately transferred to the receive FIFO. This allows for fully testing the data FIFOs without connecting to another SpaceWire node. When this bit is zero, normal operation is enabled.

<u>Link Enable</u>: When this bit is set to a one, the link connection process will be initiated. The connection state-machine will proceed to the Ready state until Start or Auto-Start is asserted. When this bit is zero, the link connection will be disabled.

<u>Link Start</u>: When this bit is set to a one, the link state-machine will move from the Ready state to the Started state and will attempt to establish a connection with another node. When this bit is zero, the state-machine will remain in the Ready state, provided it has already achieved this state. Once the state-machine has left the Ready state, this bit has no effect.

<u>Link Auto-Start</u>: The behavior of this bit is similar to Link start, however, when this bit is set and Link start is not set, the state-machine will not proceed to the Started state unless a Null character has been seen, which indicates that the other node is attempting to establish a connection. This bit allows the connection process to be cleanly initiated from one side of the link only.

<u>Packet Disable</u>: When this bit is set to a one, data is transferred without being separated into packets. No end-of-packet characters are generated or received and the packet-length FIFOs are not used. As soon as data is written to the transmit FIFO it will be sent out, provided all other conditions allow this. When this bit is zero, the data will be sent in packets. Data must be written to the transmit data FIFO <u>and</u> packet lengths must be written to the TX packet-length FIFO, before data can be transferred.

TX Almost Empty Interrupt Enable: When this bit is set to a one, an interrupt will be generated when the transmit FIFO level becomes equal or less than the value specified in the SPWR\_CHAN\_TX\_AMT register, provided the channel master interrupt enable is asserted. When this bit is zero, an interrupt will not be generated, but the status can still be read from the channel status register.

RX Almost Full Interrupt Enable: When this bit is set to a one, an interrupt will be generated when the receive FIFO level becomes equal or greater to the value specified in the SPWR\_CHAN\_RX\_AFL register, provided the channel master interrupt enable is asserted. When this bit is zero, an interrupt will not be generated, but the status can still be read from the channel status register.

RX Error Interrupt Enable: When this bit is set to a one, an interrupt will be generated when a receiver error condition is detected, provided the channel master interrupt enabled is asserted. When a zero is written to this bit, an interrupt will not be generated, but the latched status can still be read from the channel status register.

<u>Packet Received Interrupt Enable</u>: When this bit is set to a one, an interrupt will be generated when a complete packet is received, provided the channel master interrupt enable is asserted. When a zero is written to this bit, an interrupt will not be generated, but the latched status can still be read from the channel status register.

<u>Tick Received Interrupt Enable</u>: When this bit is set to a one, an interrupt will be generated when a valid time-code is received, provided the channel master interrupt enable is asserted. When a zero is written to this bit, an interrupt will not be generated, but the latched status can still be read from the Interrupt Status register.

<u>Master Interrupt Enable</u>: When this bit is set to a one all enabled interrupts for the referenced channel (except the DMA interrupts) will be gated through to the PCI host; when this bit is a zero, the interrupts can be used for status without interrupting the host.

<u>Force Interrupt</u>: When this bit is set to a one a system interrupt will occur provided the channel master interrupt enable is set. This is useful to test interrupt service routines.

<u>Write/Read DMA Interrupt Enable</u>: These two bits, when set to one, enable the interrupts for DMA write and read completion for the referenced channel. These two interrupts cannot be disabled by the master interrupt enable.

Write/Read DMA Arbitration Priority Enable: These two bits, when set to one, enable the DMA arbiter to use the TX almost empty and/or RX almost full status to give priority to a channel that is approaching the limits of its FIFOs. The levels written to the TX almost empty and RX almost full registers are used to determine these status values. When these bits are zero normal round-robin arbitration is used to determine access to the PCI bus for DMA transfers.

<u>Transmit/Receive FIFO Programmable Level Load</u>: These bits are only valid for channels with external data FIFOs. The load bits must be active during FIFO reset to select the programmable level feature. Once selected, these bits must be set to zero for normal FIFO operation. When set to one, data accesses are instead directed to the almost empty and almost full level registers (See FIFO data sheet for details).

<u>Transmit Packet-Length Repeat</u>: When this bit is set to a one, the current transmit packet-length will be used continually until there is no more transmit data or this control bit is cleared. When a zero is written to this bit, the packet-length FIFO must be read to obtain a new packet-length for each transmitted packet.

Return Valid Packet-Lengths Only Enable: When this bit is set to a one, only valid packet-lengths will be returned. If no new packet has been received since the packet-length FIFO was read, the packet-length will be returned as zero. When a zero is written to this bit and no new packet has been received since the packet-length FIFO was read, the packet-length from the last packet received will be returned. When enabled, this control allows packet-lengths to be confidently read without first checking the Receive Packet Length Valid status bit in the channel status register. This control bit was added starting with rev. J.

<u>DDR Disable:</u> For DDR equipped models this bit when set disables the port's DDR controller. The reset / default condition is enabled. To change values for segments the controller should be disabled. The new parameters entered, and then re-enabled to resume operation. It is recommended to reset the DDR after the parameters are changed to make sure the controller starts up within the defined space. See the Start/End registers for more information. *Note: the read-back value is inverted. '1' = enabled and '0' = disabled.*

<u>Time-Code Flags</u>: The time-code flags have been moved to the control register to make room for the latched almost empty/full status bits that were added to the status register. These two read-only bits are currently undefined in the SpaceWire specification and will most likely always be seen as zeros.

<u>Write/Read DMA Ready</u>: These two read-only bits report the DMA state-machine status. If they are read as a one, the corresponding DMA state-machine is idle and available to start a transfer. If the bits are read as a zero, the corresponding DMA state-machine is processing a data transfer.

#### SPWR\_CHAN\_STATUS\_0-3

[0x0054, 0x00A4, 0x00F4, 0x0144] (Status read/Latch clear write)

| Channel Status Register |                                    |

|-------------------------|------------------------------------|

| Data Bit                | Description                        |

| 31                      | Latched Receive FIFO Almost Full   |

| 30                      | Latched Transmit FIFO Almost Empty |

| 29-24                   | Time-Code Data                     |

| 23                      | Interrupt Active                   |

| 22                      | Receive Packet Length Valid        |

| 21                      | Transmit Purge Error               |

| 20                      | SpaceWire Link Established         |

| 19                      | Read DMA Error                     |

| 18                      | Write DMA Error                    |

| 17                      | Read DMA List Complete             |

| 16                      | Write DMA List Complete            |

| 15                      | TICK OUT Received                  |

| 14                      | Packet Received                    |

| 13                      | Receive Error                      |

| 12                      | Receive FIFO Overflow              |

| 11                      | Credit Error Detected              |

| 10                      | Escape Error Detected              |

| 9                       | Disconnect Error Detected          |

| 8                       | Parity Error Detected              |

| 7                       | Receive Data Valid                 |

| 6                       | Receive FIFO Full                  |

| 5                       | Receive FIFO Almost Full           |

| 4                       | Receive FIFO Empty                 |

| 3                       | Transmit Data Valid                |

| 2                       | Transmit FIFO Full                 |

| 1                       | Transmit FIFO Almost Empty         |

| 0                       | Transmit FIFO Empty                |

#### FIGURE 12

#### SPACEWIRE CHANNEL STATUS REGISTER

<u>Transmit FIFO Empty</u>: When a one is read, the transmit data FIFO for the corresponding channel contains no data; when a zero is read, there is at least one dataword in the FIFO.

<u>Transmit FIFO Almost Empty</u>: When a one is read, the number of data-words in the transmit data FIFO for the corresponding channel is less than or equal to the value written to the SPWR\_CHAN\_TX\_AMT register for that channel; when a zero is read, the level is more than that value.

<u>Transmit FIFO Full</u>: When a one is read, the transmit data FIFO for the corresponding channel is full; when a zero is read, there is room for at least one more data-word in the FIFO.

<u>Transmit Data Valid</u>: When a one is read, there is at least one word of valid transmit data. When either the transmitter or the FIFO bypass is enabled, the first word written to the transmit FIFO will be read to be available to the transmitter or the FIFO bypass circuit. Therefore although the FIFO is empty, if this bit is set, there is one additional long-word of transmit data. A zero indicates that there is no valid transmit data.

Receive FIFO Empty: When a one is read, the receive data FIFO for the corresponding channel contains no data; when a zero is read, there is at least one data-word in the FIFO.

Receive FIFO Almost Full: When a one is read, the number of data-words in the receive data FIFO for the corresponding channel is greater or equal to the value written to the SPWR\_CHAN\_RX\_AFL register for that channel; when a zero is read, the level is less than that value.

Receive FIFO Full: When a one is read, the receive data FIFO for the corresponding channel is full; when a zero is read, there is room for at least one more data-word in the FIFO.

Receive Data Valid: When a one is read, there is at least one word of valid receive data. When data is written to the receive FIFO, the first four words are read and held in latches to be ready for a PCI read DMA or single-word read. Therefore although the FIFO is empty, if this bit is set, there are as many as four additional long-words of receive data. A zero indicates that there is no valid receive data.

<u>Parity Error Detected</u>: When a one is read, it indicates that a parity error has occurred since the status was last cleared. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no parity error has occurred.

<u>Disconnect Error Detected</u>: When a one is read, it indicates that a disconnect error has occurred since the status was last cleared. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no disconnect error has occurred. A disconnect error occurs when there is no activity on the data or strobe line for 850 nanoseconds.

<u>Escape Error Detected</u>: When a one is read, it indicates that an escape error has occurred since the status was last cleared. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no escape error has occurred. An escape error occurs when an escape character is followed by anything other than an FCT or a data character.

<u>Credit Error Detected</u>: When a one is read, it indicates that a credit error occurred since the status was last cleared. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no credit error has occurred. A credit error is a violation of the SpaceWire data flow-control protocol.

Receive FIFO Overflow: When a one is read, it indicates that either an attempt has been made to write data to a full receive data FIFO or a packet-length value to a full packet-length FIFO. Neither of these conditions should occur if the data flow-control protocol is functioning correctly. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no overflow condition has occurred.

Receive Error: When a one is read, it indicates that one of the five preceding error conditions has been detected since this bit was last cleared. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no receive error has occurred.

<u>Packet Received</u>: When a one is read, it indicates that a packet has been received since this bit was last cleared. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that a packet has not been received.

<u>TICK OUT Received</u>: When a one is read, it indicates that a valid time code has been received by the referenced channel since this bit was last cleared. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that a valid time-code has not been received.

Write/Read DMA List Complete: When a one is read, it indicates that the corresponding DMA has completed. These bits are latched and must be cleared by writing the same

bit back to the channel status port. A zero indicates that the corresponding DMA has not completed.

<u>Write/Read DMA Error</u>: When a one is read, it indicates that an error has occurred while the corresponding DMA was in progress. This could be a target or master abort or an incorrect direction bit in one of the DMA descriptors. These bits are latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no DMA error has occurred.

<u>SpaceWire Link Established</u>: A one indicates that the referenced link is in the run state, which allows all types of link and normal characters to be exchanged. A zero indicates that the link is not in the run state.

<u>Transmit Purge Error</u>: When a one is read, it indicates that a connection error occurred while a transmit packet was in progress and the transmitter was unable to completely delete the remainder of the packet's data from the transmit data FIFO. This can occur if the packet-length was longer than 4 Kbytes or the packet data had not been all written to the transmit data FIFO. The link connection state-machine allows a 30 microsecond delay for purging transmit data after a link error. At 132 Mbytes/second this allows almost 4 Kbytes of data to be discarded. This bit is latched and must be cleared by writing the same bit back to the channel status port. A zero indicates that no transmit purge error has occurred.

RX packet Length Valid: When a one is read, there is at least one valid receive packet-length value available. When this bit is a zero, it indicates that there are no valid receive packet-length values.

<u>Interrupt Active</u>: When a one is read, it indicates that an enabled interrupt condition (other than the DMA interrupts) is active for the referenced channel. A zero indicates that no enabled interrupt condition is active.

<u>Time-Code Data</u>: The last time-code value received can be read from this six-bit data-field. The TICK\_OUT received status bit will indicate if the data is a new valid time-code value. A time-code is considered valid if it is one more than the previous stored value. If the time-code is the same as the stored value, it is assumed to be a duplicate resulting from a cycle in the SpaceWire network and is therefore ignored. If the time-code meets neither of these conditions, it is stored, but the TICK\_OUT signal is not asserted until the next time-code is received and is one more than that last stored value. At this point the time-code is deemed to be re-synchronized.

<u>Latched Receive FIFO Almost Full</u>: When a one is read, it indicates that the receive FIFO data count has become greater than or equal to the value in the

SPWR\_CHAN\_RX\_AFL register. A zero indicates that the FIFO has not become almost full. This bit is latched and can be cleared by writing back to the Status register with a one in this bit position.

<u>Latched Transmit FIFO Almost Empty</u>: When a one is read, it indicates that the transmit FIFO data count has become less than or equal to the value in the SPWR\_CHAN\_TX\_AMT register. A zero indicates that the FIFO has not become almost empty. This bit is latched and can be cleared by writing back to the Status register with a one in this bit position.

## SPWR\_CHAN\_FIFO\_0-3

[0x0058, 0x00A8, 0x00F8, 0x0148] Write TX/Read RX FIFO Ports

| RX and TX FIFO Ports    |                                   |  |  |

|-------------------------|-----------------------------------|--|--|

| <b>Data Bit</b><br>31-0 | <b>Description</b> FIFO Data-Word |  |  |

#### FIGURE 13

#### SPACEWIRE CHANNEL RX/TX FIFO PORTS

These ports are used for single-word accesses into the channel TX FIFO and out of the channel RX FIFO.

### SPWR\_CHAN\_WR\_DMA\_PNTR\_0-3

[0x005C, 0x00AC, 0x00FC, 0x014C] Write only

| ı                       | nput DMA Pointer Address Port                                 |

|-------------------------|---------------------------------------------------------------|

| <b>Data Bit</b><br>31-0 | <b>Description</b> First Chaining Descriptor Physical Address |

## FIGURE 14

#### SPACEWIRE CHANNEL WRITE DMA POINTER PORT

This write-only port is used to initiate a scatter-gather write [TX] DMA. When the address of the first chaining descriptor is written to this port, the DMA engine reads three successive long words beginning at that address. Essentially this data acts like a chaining descriptor value pointing to the next value in the chain.

The first is the address of the first memory block of the DMA buffer containing the data to read into the device, the second is the length in bytes of that block, and the third is

the address of the next chaining descriptor in the list of buffer memory blocks. This process is continued until the end-of-chain bit in one of the next pointer values read indicates that it is the last chaining descriptor in the list.

All three values are on LW boundaries and are LW in size. Addresses for successive parameters are incremented. The addresses are physical addresses the HW will use on the PCI bus to access the Host memory for the next descriptor or to read the data to be transmitted. In most OS you will need to convert from virtual to physical. The length parameter is a number of bytes, and must be on a LW divisible number of bytes.

Status for the DMA activity can be found in the channel control register and channel status register.

#### Notes:

- 1. Writing a zero to this port will abort a write DMA in progress.

- 2. End of chain should not be set for the address written to the DMA Pointer Address Register. End of chain should be set when the descriptor follows the last length parameter.

- 3. The Direction should be set to '0' for Burst In DMA in all chaining descriptor locations.

- 4. The segment size is 31-0 however the byte count is shifted down two positions to create a LW count in memory. This means the actual count is 1G-1 [4Gbytes minus 1 LW] or xFFFFFFC for the max byte count.

## SPWR\_CHAN\_TX\_FIFO\_COUNT\_0-3

[0x005C, 0x00AC, 0x00FC, 0x014C] TX FIFO Data Count (read only)

|          | TX FIFO Data Count                        |

|----------|-------------------------------------------|

| Channel  | ls with External TX Data FIFOs            |

| Data Bit | Description                               |

| 31-20    | Number of TX Packet-Length Values Stored  |

| 19-0     | Number of TX Data-Words Stored            |

| Channe   | Is with Internal TX Data FIFOs            |

| 31-20    | Number of TX Packet-Length Values Stored  |

| 19-14    | Spare                                     |

| 13-0     | Number of TX data-Words Stored            |

| Type 4 c | lesigns report                            |

| 31-20    | Number of TX Packet-Length Values Stored  |

| 19-14    | Spare                                     |

| 9-0      | Number of TX data-Words Stored in IO FIFO |

|          |                                           |

#### FIGURE 15 SPACEWIRE CHANNEL TX FIFO DATA COUNT PORT